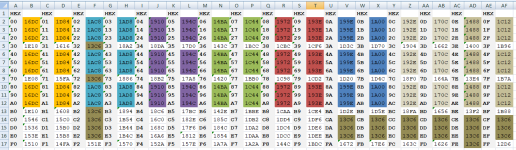

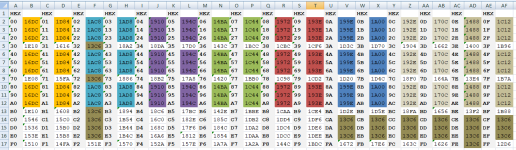

Ok, whatever instruction set the BASIC NX ROS contains, I stepped through a few dozen of them on the 5110 ROS to get a general feel for the operands they contain.

I did this by issuing a simple BASIC statement ("10 A=8") and then trapped each time the PALM code did a GETB Rxx, $1 after that -- i.e. extracted each byte that was requested out of the BASIC NX ROS (and the emulator keeps track of the current address offset into that NX ROS).

So the first byte in each row in the following corresponds to some opcode that is being processed. We've always assumed it was some System/3 instructions, but we're not sure. It could be a later post-1970 model of System/3, or some "extended mnemonic" variant that we're not familiar with.

The addresses (0924, etc) are in the BASIC NX ROS (unless otherwise specified).

Code:

0920: C3 00 0B 22

(start of BASIC NX ROS in support of "10 A=8" BASIC statement)

0924: C8 20 0B 2A 05 C4

CA 0F 0B 2A 23 EE

3B 10 0B 6C

38 80 0B A1 04 9F

31 00 0B A8 (not executed, appears to be in support of prior instruction or is skipped)

3C 40 05 C0

3C 00 0B 57

09 01 0B 58 00 00

3B 10 0B 6D

3B 08 0B A4

33 40 01 3F

3C FF 10 CE (set RWS[10CE] == FF)

04 40 10 CF 10 CE (copy RWS[10CE] into 10CF, looks like 5x64 times -- not sure how this knows to do this more than 40h/64dec times)

3B 04 0B 6D

35 40 0B 63

33 50 00 03

F8 40 50

C0 A0 04 D5

C4 40 0B 61

08 04 D5 (not executed, appears to be in support of prior instruction or is skipped)

34 40 0B AC

3B 03 0B AD

0C 01 0B AA 0D B0

3B 03 0B AB

33 40 06 07

34 40 0B B2

33 40 00 04

36 40 0B AC

C0 A0 04 D5

C4 40 0B AA

18 04 E1 (not executed, appears to be in support of prior instruction or is skipped)

---------------------- jump to 0x09C2

09C2: 3B 04 0B 6D

09 03 0B A6 00 00

0C 03 0B AE 0B A6

33 00 06 07

34 00 0B B0

30 04 0B AA --> leads to the BRA table at 0x217E in the BASIC ROS (3rd offset) that targets 0x20BC

BASIC ROS 20BC: perform data movement (using PALM), then finally JMP ($0104) to start processing the next BASIC NX instruction at 09DE

09DE: 33 40 00 05

33 10 05 80

33 30 05 BF

F1 05 F4

------------------------------ jump to 0x0BE8

0BE8: 34 80 0F D9

33 30 05 C0

DD 40 00 06 01

33 ...

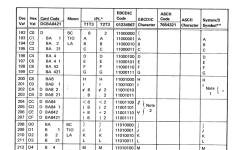

Using SC21-7509-7_System3_Basic_Assembler_Reference_Manual as a reference (

here), Appendix A, my understanding is that for the System/3, the second half of the opcode-byte is a kind of "opcode category". Like 07-A7 (or any "x7" series) is a variant of the "SZ" instruction. So, I grouped the set of opcodes covered above ordered by the second byte. There may be a newer version of this reference manual that is not yet digitized, or IBM took liberties at having some extended or "undocumented" opcodes. A lot of these opcodes do jive with the manual, but for example there are no "3-series" opcodes (e.g. "33") - since this is from the 5110, it's possible that was added after 1975.

30 SNS (page 66)

C0 BC (page 66)

F1 APL (page 68)

33 ????

04 ZAZ (page 53)

34 ST (page 65)

C4 ZAZ-extended??? (page 53)

35 L (page 65)

36 A (page 65)

C8 TBN-extended??? (page 64)

38 MVX or TBN-extended??? (page 56)

F8 MVX-extended??? (page 56)

09 TBF-extended??? (page 64)

CA SBN-extended??? (page 63)

3B SBF (page 64)

3C MVI (page 63)

0C MVC-extended??? (page 63)

DD CLC-extended??? (page 58)

Anyhow, I'm pretty confident none of that is PMC (pseudo machine code stuff). At least not as described in 3-277 in

here . Pseudo code may still be involved, TBD. But at least some form of System/3 native does seem to be involved, and the emulator provides a method for isolating out the exact addresses/ROS offsets involved.