voidstar78

Veteran Member

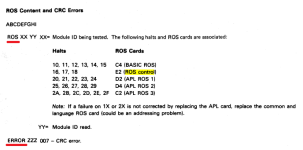

Greetings! I'm trying to figure out the arrangement of ROS code in the IBM 5100.

@stepleton extracted these ROS' a while back with a very clever process (and did it twice to ensure accuracy!).

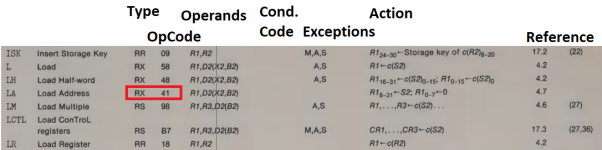

I'm not quite old enough to have worked on these systems first hand in their heyday, so I am just going by what I can read from the IBM manuals. But I am fairly familiar with the 5110 emulator and the extracted ROS binaries from that system (see 5110VEMU). From what I've read, the PALM processor was unchanged between the IBM 5100 and 5110 (in terms of opcodes and what they do). Keyboard scancodes and video characterset codes were changed, but it's the same 16-bit PALM (16x16-bit registers across 4 interrupt levels -- well, 3 plus a main processing tier).

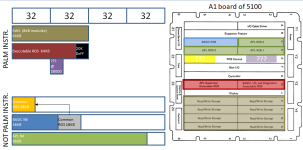

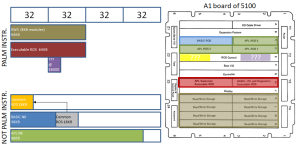

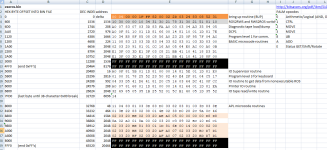

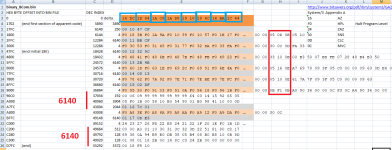

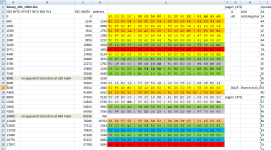

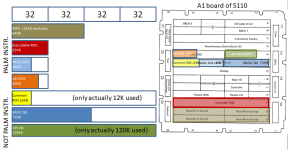

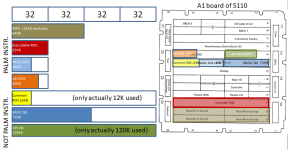

Let me begin with the 5110, as an initial frame of reference. Based on my understanding, it has a ROS arrangement like this:

What was extracted (by Christian Corti, who I've tried to contract but so far unable to reach) were 6 binaries files: executive ros, common ROS, BASIC ROS, BASIC NX ROS, APL ROS, and APL NX ROS.

These are in two categories: basically native PALM instruction binaries, and then non-PALM binaries (which my understanding those were essentially binaries extracted from System/370 and System/3 -- or variants thereof -- or at least existing BASIC and APL interpreted programs from those corresponding systems). This is partly why these IBMs were "slow" - they were emulating the running of interpreters! But to me it's also very clever -- software is hard/expensive to produce, difficult to debug/perfect (especially at a time when you didn't have interactive debuggers, and had to wait for printers, etc.).

Ok, back to the question: I have reason to believe the "ROS" (ROM) code can only be 32 Kbytes (because in the emulator they shift a bit when addressing the ROS, which means the ROS' end up only 15-bit addressed, or 32K). Or maybe that was just a side effect of having extracted the ROS' into individual files - I'm not 100% sure.

The "NX" code can be up to 128KB, as they seem to be 16-bit addressed and 16-bits wide (the core emulator code reserves up to this space, but most of these NX ROS's don't actually use that much). And the ROS PALM code has to do a lot of bit twiddling to feed things in and out of that "NX" code.

NOTE, for this exercise I'm ignoring the Feature ROS. We can access it and could extract it, but it's a component of (apparently) very little interest -- related to disk sorting (I think maybe sorting content that's on a disk? which yes by itself is useful, but not relevant until you get to a working disk setup).

Both APL and BASIC have both a "ROS" and an "NX" (non-executive) binary. The "ROS" is the PALM-native code that coordinates the corresponding emulated code (the BASIC interpreter, or the APL interpreter). The PALM by itself seems to be a fairly capable processor, so it's a shame its raw capabilities were so hidden. I'm not sure if any "pure-assembly" (machine-code) programs were ever commercially developed for it (although I've read about some IMF code that could be latched in from the DCP, maybe those were in PALM opcodes?)

Anyhow, there is quite a bit of content/code in the "Common ROS", but frankly I haven't been able to quite determine if it is PALM instructions or a mix of System/370 and System/3 content?? Somewhere i've read that the Common ROS stores "common tables" between the emulated code (I suspect maybe conversion codes for maybe effectively scancodes and characterset codes of those emulated systems, and the native ones of the IBM5100/5110? so the "code" in the common ROS could just be lookup tables -- but it's 12K of "something", the remaining 4K is all blank/zeros -- and remember the Common ROS is read-only, ROS/ROM, not a scratch pad space).

If you removed both BASIC and APL - you still have a functional machine: you have the Executive ROS, that can run PALM instructions from the RWS/RAM. BUT, if you want to load or save content, you have to be be savvy and send proper IOCB control codes and branch to the proper executive microcode (so the Executive ROS is exactly like an early BIOS. But imagine you're in BASIC or APL and do a "SAVE" or ")SAVE" command, something has to interpet what the emulator would do, and communicate that back as suitable IOCB control codes -- I'm not sure if the "Common ROS" handles that, or parts of that, or not (which is why possibly it could be a mix of "all of the above" PALM and System/370/3 code, or either).

From my emulator, "between" each BASIC or APL statement (after pressing ENTER/ATTN), control temporarily goes back to the Executive ROS - to do maintenance things like scroll the screen, update the RWS available RAM count, blink the cursor, check for interrupts, etc. This applies when running code also - run a statement, swap back to Executive, check status, repeat next line, etc.

NOTE, in the above Card F is marked "ROS Control" or also cited as "Common and Language ROS" - the 5110 was offered in an "A" version that (allegedly) didn't have BASIC. So I'd expect the BASIC ROS and BASIC NX portions of that slot to just be missing, the Common ROS should still be there, and the language switch just hard-wired to an APL startup. Not sure. Also don't quote me on the arrangement of those ROS across Card F - I just guessed. I don't know which "side" is 0 address (if that even makes any sense). Remember as 16-bit words (or maybe 18-bit w/ parity?), the BASIC NX should be "36K" addressed (2 bytes each, total 72K).

This is just the setup to the question, which is the next post...

@stepleton extracted these ROS' a while back with a very clever process (and did it twice to ensure accuracy!).

I'm not quite old enough to have worked on these systems first hand in their heyday, so I am just going by what I can read from the IBM manuals. But I am fairly familiar with the 5110 emulator and the extracted ROS binaries from that system (see 5110VEMU). From what I've read, the PALM processor was unchanged between the IBM 5100 and 5110 (in terms of opcodes and what they do). Keyboard scancodes and video characterset codes were changed, but it's the same 16-bit PALM (16x16-bit registers across 4 interrupt levels -- well, 3 plus a main processing tier).

Let me begin with the 5110, as an initial frame of reference. Based on my understanding, it has a ROS arrangement like this:

What was extracted (by Christian Corti, who I've tried to contract but so far unable to reach) were 6 binaries files: executive ros, common ROS, BASIC ROS, BASIC NX ROS, APL ROS, and APL NX ROS.

These are in two categories: basically native PALM instruction binaries, and then non-PALM binaries (which my understanding those were essentially binaries extracted from System/370 and System/3 -- or variants thereof -- or at least existing BASIC and APL interpreted programs from those corresponding systems). This is partly why these IBMs were "slow" - they were emulating the running of interpreters! But to me it's also very clever -- software is hard/expensive to produce, difficult to debug/perfect (especially at a time when you didn't have interactive debuggers, and had to wait for printers, etc.).

Ok, back to the question: I have reason to believe the "ROS" (ROM) code can only be 32 Kbytes (because in the emulator they shift a bit when addressing the ROS, which means the ROS' end up only 15-bit addressed, or 32K). Or maybe that was just a side effect of having extracted the ROS' into individual files - I'm not 100% sure.

The "NX" code can be up to 128KB, as they seem to be 16-bit addressed and 16-bits wide (the core emulator code reserves up to this space, but most of these NX ROS's don't actually use that much). And the ROS PALM code has to do a lot of bit twiddling to feed things in and out of that "NX" code.

NOTE, for this exercise I'm ignoring the Feature ROS. We can access it and could extract it, but it's a component of (apparently) very little interest -- related to disk sorting (I think maybe sorting content that's on a disk? which yes by itself is useful, but not relevant until you get to a working disk setup).

Both APL and BASIC have both a "ROS" and an "NX" (non-executive) binary. The "ROS" is the PALM-native code that coordinates the corresponding emulated code (the BASIC interpreter, or the APL interpreter). The PALM by itself seems to be a fairly capable processor, so it's a shame its raw capabilities were so hidden. I'm not sure if any "pure-assembly" (machine-code) programs were ever commercially developed for it (although I've read about some IMF code that could be latched in from the DCP, maybe those were in PALM opcodes?)

Anyhow, there is quite a bit of content/code in the "Common ROS", but frankly I haven't been able to quite determine if it is PALM instructions or a mix of System/370 and System/3 content?? Somewhere i've read that the Common ROS stores "common tables" between the emulated code (I suspect maybe conversion codes for maybe effectively scancodes and characterset codes of those emulated systems, and the native ones of the IBM5100/5110? so the "code" in the common ROS could just be lookup tables -- but it's 12K of "something", the remaining 4K is all blank/zeros -- and remember the Common ROS is read-only, ROS/ROM, not a scratch pad space).

If you removed both BASIC and APL - you still have a functional machine: you have the Executive ROS, that can run PALM instructions from the RWS/RAM. BUT, if you want to load or save content, you have to be be savvy and send proper IOCB control codes and branch to the proper executive microcode (so the Executive ROS is exactly like an early BIOS. But imagine you're in BASIC or APL and do a "SAVE" or ")SAVE" command, something has to interpet what the emulator would do, and communicate that back as suitable IOCB control codes -- I'm not sure if the "Common ROS" handles that, or parts of that, or not (which is why possibly it could be a mix of "all of the above" PALM and System/370/3 code, or either).

From my emulator, "between" each BASIC or APL statement (after pressing ENTER/ATTN), control temporarily goes back to the Executive ROS - to do maintenance things like scroll the screen, update the RWS available RAM count, blink the cursor, check for interrupts, etc. This applies when running code also - run a statement, swap back to Executive, check status, repeat next line, etc.

NOTE, in the above Card F is marked "ROS Control" or also cited as "Common and Language ROS" - the 5110 was offered in an "A" version that (allegedly) didn't have BASIC. So I'd expect the BASIC ROS and BASIC NX portions of that slot to just be missing, the Common ROS should still be there, and the language switch just hard-wired to an APL startup. Not sure. Also don't quote me on the arrangement of those ROS across Card F - I just guessed. I don't know which "side" is 0 address (if that even makes any sense). Remember as 16-bit words (or maybe 18-bit w/ parity?), the BASIC NX should be "36K" addressed (2 bytes each, total 72K).

This is just the setup to the question, which is the next post...

Last edited: