Received more parts of the emulator and am now able to put much of it together. Also have been working on a tester, which is more important than I originally realized. It's the same concept that

@PDP11GY described, use the emulator platform as a tester. The RK05 bus has 20 inputs and 18 outputs so most of the hardware is already there. I wish I'd put another SN75452 package on the emulator to have 20 in and 20 out. Decided to use a dipswitch on an external board to implement part of the drive select signaling while I'm short 2 driver outputs on this board. On rev 2 the extra SN75452 can be added. I'm thinking that maybe a configurable drive tester/disk reader-copier might also be a useful device. That isn't where I started though.

So, some photos... views of the front. With about 1/3 the width and height, there's not much room for anything but switches and lights.

It's intended to behave as much like a real RK05 as possible, just smaller. Run/Load switch does the same, it loads and unloads the microSD. WT PROT is momentary and works like the original, too. A small servo motor moves the microSD away from view so it can't be removed while running. There's an empty hole there right now. The microSD carrier is almost complete and prototyped but I don't yet have a nice one to install. All 8 lights indicate the same as an RK05. The Fault light is white on this one. I'm considering the purchase of a reel of translucent red filament for the Fault light diffuser but it might take forever to use all of that filament. Maybe white is okay. The diffuser block is printed as all 8 together in a frame and it's easy to cut one out and install a red color diffuser in the upper right corner. The small display to the right of the lights indicates the drive number as 0 through 7 or 0/1 through 6/7 for the "RK05f" version. Also short-duration messages will appear in the display while loading and unloading, and errors if the microSD has bad files, can't be read or isn't inserted, etc.

There's a 4-position piano-style dipswitch on the board just behind the front panel. You can see the "Device Select". Dipswitches just arrived this evening, haven't installed them yet.

Side view on the left, the front panel electronics board can be seen. Rocker switches are quite deep and there are cutouts on this board for the switches to poke through. The main emulator board is on the back of the stack. The white bezel is 3D printed and holds everything together. M3 threaded inserts are heat staked into the four posts on the corners of the bezel.

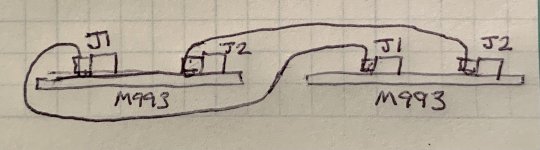

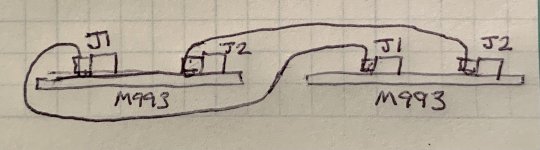

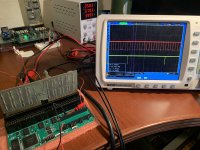

Each photo shows a tester cabled to an emulator. Almost the same hardware for each, I'll explain. Photo on the left shows the two standard RK05 slots, one with a terminator and behind that is an adapter board with cables. This is almost like the M993 but with 40-pin header connectors and with an adapter board at each end can be used to extend the RK05 bus to additional drives. There's a little non-standard thing with the BUS_RK11D_L signal so it can also extend to more drives in a PDP-11 system that use the binary encoded drive selection method. The black flat-cable clamp is a 3D printed piece... quite simple. This doesn't have all of the Unibus signals but does have all RK05 signals. The pinout of the two 40-pin cables is also set up to plug into an RK8-E controller. I see that the RPI-Pico is currently missing from the tester board... not intended.

The photo on the right is the other side of the configuration seen on the left. The board on the left of the right-hand photo is the emulator and the board on the right with the blue-wire rat's-nest is the tester. The blue wires route the drivers on the tester to signals that are receivers on the emulator, and vice versa. This is the only blue-wire version that I'll ever make. If there's interest in a drive tester then a PCB will be designed. The board in front with 3 holes in it is the front-panel electronics which connects to the main emulator board via a 20-pin flex. There's also a tiny 8-pin flex that connects from the emulator to a microSD socket that's on the front panel. This microSD on the front panel is just something for the prototype so I'd have a way to connect a micoSD for debugging. The next version of the front-panel electronics will have this socket and flex connector removed and they'll be on a separate tiny board that mounts to the microSD carriage that tilts out of the way when the "disk" is loaded.

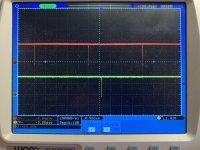

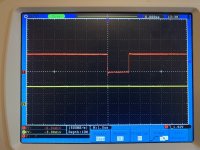

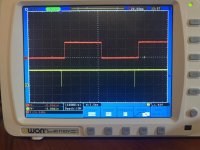

Just recently completed design and unit testing of the Verilog for the tester FPGA. It'll be fun to pair this with the emulator. In a prior post there were scope traces of the emulator generating sector and index pulses, but now we get to more fun stuff with reading and writing data, confirming the disk read/write timing and CPU interface.

) Roland's clone of the M993: https://github.com/Roland-Huisman/Digital-M993-RK05-connector-board/tree/master

) Roland's clone of the M993: https://github.com/Roland-Huisman/Digital-M993-RK05-connector-board/tree/master