dave_m

Veteran Member

Can anyone

recommend an inexpensive FPGA for that purpose with many IO pins?

Thomas,

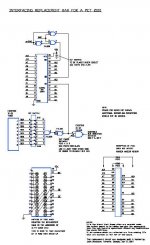

A small board called the PETVet uses an ATMEGA644 AVR chip and has done everything you need. I'd advise anyone with the old style ROMs and RAMs (6540 and 6550) on their model 2001 PETs to get one and save a lot of time trying to replace those "impossible to get" parts. See: PETVet from bitfixer.com. Mike also has a great PETDisk gadget for the IEEE bus. That is the easiest way to get PET programs from the internet into your old PET as it uses a PC compatible SD memory card. I am a happy user of these gadgets and can vouch for them.

-Dave