Suddenly, I had an idea that if I were to successfully reproduce PDP-11/70, I would provide an accurate list of backplane connections that could serve as a test pattern.

By checking each connection one by one according to this list, We could determine if all connections were correct

This way, the coverage rate can be 100%

The 11/70 backplane got up to revision T. Revisions L and later have an etch that replaces critical signals carried on regular yellow wire (and a ground pin in the etch) to a twisted pair of black and white wire. So, even if you create a complete list of interconnects, you'll still be missing which ones need to be routed specially or done with twisted pair.

There are also a bunch of signals that go from one board to another, something gets done, and the signals come back to the first board. That's just because the necessary components overflowed the available board space, given early 1970's design constraints. Stuff got shipped off to free space on another board, then comes back without it being used for anything else on the other board, just because the other board had free space.

Consider the never-marketed KE74 CIS option for the 11/74 (the 11/70 + CIS, not the 11/70-MP that got renamed to the 11/74 when the CIS option was stopped). I believe the plan was to double the capacity of the existing microcode ROMs, keeping essentially the same microcode (aside from dispatching the CIS instructions) but adding some or all of the CIS microcode. I don't know if that was for the "simple" CIS instructions that would be handled by the existing 11/70 CPU, assist for dispatching to the KE74, or the entire KE74 control store (I doubt that, given the complexity of the control store on the KE44). In any event, with one of the Massbus slots re-purposed for holding the CIS board set, that would have been a lot of new, long signal cables between the Massbus slot and the control store area of the CPU.

In any event, "re-creating" the 11/70 CPU is sort of the same dilemma VSI faced when initially announcing their intent to port VMS to the x86-64 architecture. I asked if the goal was:

1) To preserve feature, syntax and bug compatibility with earlier VMS systems (essential for customers who wanted to get off Itanium or Alpha VMS with a minimum of fuss, and hopefully avoiding recompilation)

2) Implement modern compilers to attract customers new to VMS (essential, because they want to take their Linux/whatever code and run it on VMS to take advantages of features like clustering without re-writing into ancient language dialects). As someone who tried building Perl on VAX/VMS, I can tell you it is not simply "./configure; make" as it is on Linux.

3) Some combination of the two, since the installed base is by definition a shrinking market. How fast it is shrinking is unknown, probably even to VSI, because their only view into it is how many support contracts they'd sold for Alpha and Itanium VMS.

Those are three mostly-incompatible goals (#3 requires a C compiler that accepts both "/STANDARD=VAXC" and also the latest c++ extensions, or maintaining two separate compilers, with the same being true for Fortran and Cobol, at least. I'm unsure of the issues with Pascal, and DEC-ish BASIC is pretty much unique to VMS).

Getting back to your 11/70, we can assume that the goals are:

1) Talk to the original front panel or a faithful replica

2) Execute the original microcode faithfully

3) Support (some subset of) real 11/70 periplerals

4) Allow execution at both "real 11/70" speed as well as a "turbo" speed of whatever the new hardware can run reliably at

5) (Maybe) Add CIS and the 11/93 TOY clock as well as memory battery backup

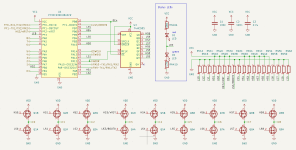

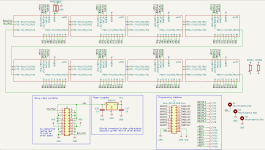

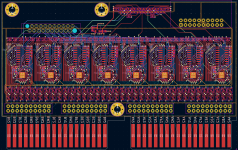

You can do that by re-creating the original boards and backplane (a huge amount of work), implement the same logic using modern components (possibly with physically smaller boards w/ SMD components, a smaller number of boards, or both). Let's face it almost none of the people who "want" an 11.70 have either the space for it or the desire to pay the power bill for running it. Look at how successful the PiDP-11 has been, even though it is a miniature front panel with a Raspberry Pi running simh behind it. SO you're going to have to miniatureize it somehow.