Hello,

A few months ago we bought a Commodore PET 2001-N in a known-to-be-not-working condition. It had, apparently, spent the last 30 years of it's life hiding in a loft and copious dust and rust bears that out. I have fixed several problems so far (see the end of this post, in case it is relevant), but I have 3 problems that I cannot solve. For the first problem, I think that I have come to the point of having to test the CPU, RAM and ROM but I want to make sure I haven't missed anything else first.

The 3 symptoms:

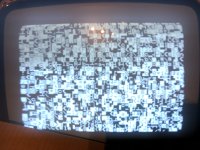

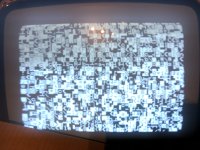

1. Garbled screen (see picture)

2. The display goes to black after about 3 minutes. It recovers after being switched off for a few minutes, so I'm suspecting a thermal problem.

3. The display is slightly truncated at the top. (See picture). It is completely alleviated by reducing brightness to minimum.

My observations:

-The +5V, -5V and +12V regulated rails are all within 2% of what is expected.

-All 6332 ROMs at D6-D9 and F10 have about 4.9V at pins 21+24, and all are quite hot to the touch (although D7 is notably cooler).

-All RAMs (now) have -5.1V and are all cold to the touch.

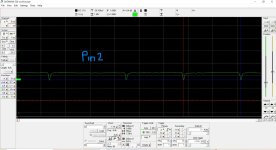

-The 555 reset output (Pin 2) toggles Low - High - Low at switch on.

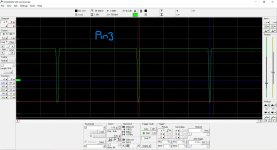

-The CPU reset Pin 40 is held low for about 1 second at switch on (Pin 40 goes: Low -> High, not High -> Low - > High)

-The CPU is warm to touch

Is the behaviour at CPU Pin 40 correct? Or should it be High -> Low - > High?

I have a logic probe and oscilloscope and a basic knowledge of electronics (although that last point depends on your benchmark, I suppose).

Here is a brief my-PET history, in case it turns out to be relevant:

I have found and repaired these problems so far:

1. The -5V rail was unstable and reducing to -7V (>>> replaced VR6 and then Diode CR13)

2. There was no vertical sync (single horizontal white line) (>>> replaced G10 and H10).

3. There was originally 0V at ROM D7 and D8. (>>> reseated chips)

4. Repaired cut track (INIT line to H1 Pin 12)

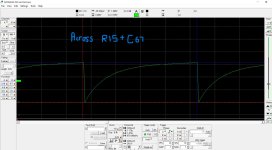

I have also replaced Capacitor C62, as I had one.

I suppose the first thing is to ask whether the CPU reset pin behaviour is as expected...?

Thanks

Justin

(UK, Norfolk)

A few months ago we bought a Commodore PET 2001-N in a known-to-be-not-working condition. It had, apparently, spent the last 30 years of it's life hiding in a loft and copious dust and rust bears that out. I have fixed several problems so far (see the end of this post, in case it is relevant), but I have 3 problems that I cannot solve. For the first problem, I think that I have come to the point of having to test the CPU, RAM and ROM but I want to make sure I haven't missed anything else first.

The 3 symptoms:

1. Garbled screen (see picture)

2. The display goes to black after about 3 minutes. It recovers after being switched off for a few minutes, so I'm suspecting a thermal problem.

3. The display is slightly truncated at the top. (See picture). It is completely alleviated by reducing brightness to minimum.

My observations:

-The +5V, -5V and +12V regulated rails are all within 2% of what is expected.

-All 6332 ROMs at D6-D9 and F10 have about 4.9V at pins 21+24, and all are quite hot to the touch (although D7 is notably cooler).

-All RAMs (now) have -5.1V and are all cold to the touch.

-The 555 reset output (Pin 2) toggles Low - High - Low at switch on.

-The CPU reset Pin 40 is held low for about 1 second at switch on (Pin 40 goes: Low -> High, not High -> Low - > High)

-The CPU is warm to touch

Is the behaviour at CPU Pin 40 correct? Or should it be High -> Low - > High?

I have a logic probe and oscilloscope and a basic knowledge of electronics (although that last point depends on your benchmark, I suppose).

Here is a brief my-PET history, in case it turns out to be relevant:

I have found and repaired these problems so far:

1. The -5V rail was unstable and reducing to -7V (>>> replaced VR6 and then Diode CR13)

2. There was no vertical sync (single horizontal white line) (>>> replaced G10 and H10).

3. There was originally 0V at ROM D7 and D8. (>>> reseated chips)

4. Repaired cut track (INIT line to H1 Pin 12)

I have also replaced Capacitor C62, as I had one.

I suppose the first thing is to ask whether the CPU reset pin behaviour is as expected...?

Thanks

Justin

(UK, Norfolk)

Last edited: