GloriousCow

Experienced Member

- Joined

- Oct 28, 2022

- Messages

- 71

Ah, so there is a distributed output port. Interesting.

It's a pretty interesting design. Each graphics controller reads from two planes and contributes two bits to the attribute controller, which takes the final 4 bits and applies the palette. At least, that's how it works in graphics mode.

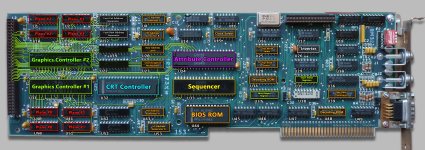

I made this diagram for a future blog post / video on the EGA card:

The sequencer produces the RAM timings and CAS/RAS signals for all 4 planes of RAM. Interestingly this is how the map mask register is implemented - by withholding the right strobe, the sequencer can prevent writes to certain planes.

If you look at the registers in isolation from a reference book, it can feel a bit disorganized, and there is repeated functionality. It makes sense when you realize that the registers exist on different chips with no way to communicate or synchronize register state; so you must set up multiple chips for the same mode, sometimes.

Last edited: