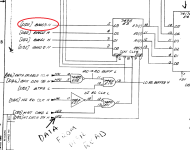

Today have been able to reliably reproduce the "Disk Address Register Error". It seems that this error only occurs once after power-up. Subsequent runs of the diagnostics do not fail with this specific error condition. Earlier I suspected that the sector & side storage in E96 is failing with bit 1 of the sector address being stuck high. I have now written two small self contained diagnostic programs which prove that the sector address and side is correctly stored and with the subsequent DMAN IOTs it is correctly clocked out on pin 10 of E96.

Here is the first which in a more comprehensible form replicates the maindec-08-dhrka-e-pb test starting at address 0547:

Code:

1 / RK05 DIAGNOSTIC

2 DSKP=6741

3 DCLR=6742

4 DLAG=6743

5 DLCA=6744

6 DRST=6745

7 DLDC=6746

8 DMAN=6747

9

10 *20

11 000020 0020 K0020, 0020

12 000021 0200 K0200, 0200

13 000022 1000 K1000, 1000

14 000023 4000 K4000, 4000

15

16 *200

17 000200 7301 START, CLA CLL IAC / AC = 1, LINK=0

18 000201 6742 DCLR / CLEAR AC AND CONTROLLER

19 000202 7240 CLA CMA / AC = 7777

20 000203 6743 DLAG / DISK ADDRESS REGISTER = 7777

21 000204 7200 CLA / AC = 0

22 000205 6743 DLAG / DISK ADDRESS REGISTER = 0000

23

24 000206 7330 CLA CLL CML RAR / AC = 4000, LINK = 0

25 000207 6747 DMAN / ENTER MAINTENANCE MODE

26 000210 7010 RAR / AC = 2000

27 000211 6747 DMAN / ENABLE SHIFT TO DATA BUFFER RANK 4 (DB4)

28 000212 7300 CLA CLL / AC = 0000, LINK = 0

29

30 000213 1022 TAD K1000 / ENABLE SHIFT CRC

31 000214 1021 TAD K0200 / ENABLE SHIFT SECTOR + SURFACE

32 000215 6747 DMAN / SHIFT SECTOR 5 TIMES

33 000216 6747 DMAN / 2

34 000217 6747 DMAN / 3

35 000220 6747 DMAN / 4

36 000221 6747 DMAN / 5

37

38 000222 7300 CLA CLL

39 000223 1022 TAD K1000 / ENABLE SHIFT CRC

40 000224 6747 DMAN / SHIFT DA 7 TIMES

41 000225 6747 DMAN / 2

42 000226 6747 DMAN / 3

43 000227 6747 DMAN / 4

44 000230 6747 DMAN / 5

45 000231 6747 DMAN / 6

46 000232 6747 DMAN / 7

47

48 000233 7300 CLA CLL

49 000234 1020 TAD K0020 / READ DATA BUFFER TO AC

50 000235 6747 DMAN / ..

51

52 000236 7402 FINISH, HLT / Normal good halt

53 000237 5200 JMP START

54 $

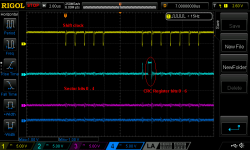

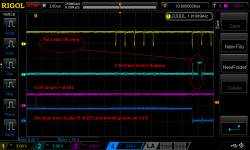

After power-on the program above nicely reproduces the error just like maindec-08-dhrka-e-pb. With scope probes on E96 /CLR, CLK, D and QE I see the correct data being stored and subsequently shifted out on QE.

The following program is a refinement of the above where it loads 4 different data patterns into the disk address register and then clocks them out (only the 5 low order bits go into E96):

Code:

1 / RK05 DIAGNOSTIC

2 DSKP=6741

3 DCLR=6742

4 DLAG=6743

5 DLCA=6744

6 DRST=6745

7 DLDC=6746

8 DMAN=6747

9

10 *20

11 000020 0020 K0020, 0020

12 000021 0200 K0200, 0200

13 000022 1000 K1000, 1000

14 000023 4000 K4000, 4000

15 000024 5252 K5252, 5252

16 000025 2525 K2525, 2525

17

18 *200

19 000200 7301 START, CLA CLL IAC / AC = 1, LINK=0

20 000201 6742 DCLR / CLEAR AC AND CONTROLLER

21 000202 7300 LOOP, CLA CLL

22 000203 1025 TAD K2525 / 2525

23 000204 4215 JMS LDRD

24 000205 7300 CLA CLL

25 000206 1024 TAD K5252 / 5252

26 000207 4215 JMS LDRD

27 000210 7340 CLA CLL CMA / 7777

28 000211 4215 JMS LDRD

29 000212 7300 CLA CLL / 0000

30 000213 4215 JMS LDRD

31 000214 5202 JMP LOOP

32

33 000215 7402 LDRD, HLT

34 000216 6743 DLAG / DISK ADDRESS = AC

35 000217 7330 CLA CLL CML RAR / AC = 4000, LINK = 0

36 000220 6747 DMAN / ENTER MAINTENANCE MODE

37 000221 7010 RAR / AC = 2000

38 000222 6747 DMAN / ENABLE SHIFT TO DATA BUFFER RANK 4 (DB4)

39 000223 7300 CLA CLL / AC = 0000, LINK = 0

40

41 000224 1022 TAD K1000 / ENABLE SHIFT CRC

42 000225 1021 TAD K0200 / ENABLE SHIFT SECTOR + SURFACE

43 000226 6747 DMAN / SHIFT SECTOR 5 TIMES

44 000227 6747 DMAN / 2

45 000230 6747 DMAN / 3

46 000231 6747 DMAN / 4

47 000232 6747 DMAN / 5

48

49 000233 7300 CLA CLL

50 000234 1022 TAD K1000 / ENABLE SHIFT CRC

51 000235 6747 DMAN / SHIFT DA 7 TIMES

52 000236 6747 DMAN / 2

53 000237 6747 DMAN / 3

54 000240 6747 DMAN / 4

55 000241 6747 DMAN / 5

56 000242 6747 DMAN / 6

57 000243 6747 DMAN / 7

58

59 000244 7300 CLA CLL

60 000245 1020 TAD K0020 / READ DATA BUFFER TO AC

61 000246 6747 DMAN / ..

62

63 000247 7402 HLT / Normal good halt

64 000250 7301 CLA CLL IAC / AC = 1, LINK=0

65 000251 6742 DCLR / CLEAR AC AND CONTROLLER

66 000252 5615 JMP I LDRD

67 $

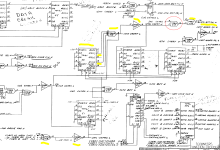

So all this means is that E96 is off the hook. The problem happens somewhere later where the data is shifted into Data Buffer Register 4. Unfortunately the data buffers are a very complex part of the circuit.

Earlier I have forced the diagnostics past the "Disk Address Register Error" and the "CRC Register Error" and found many problems all pointing to the Data Buffer Registers. So it may well be that a big chunk of errors disappear once I fixed the apparent problem in the Data Buffer Registers.