nikola-wan

Veteran Member

VintageTek Museum in Oregon has a Tektronix 4054A computer with Option 30 Dynamic Graphics coprocessor that they have been restoring.

What works:

What fails:

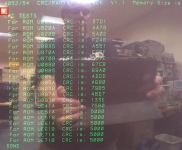

The error message after the Option 30 MEMORY TEST is NOT a problem with the Option 30 MEMORY, it is listed in the 4052 Diagnostic ROM Pack manual page 18 as happening after the test if the 4054A only has 32KB of RAM:

What is an error in the Option 30 MEMORY test photo is the GREEN dot above the OPT 30 TESTS - this should be a blinking cursor rectangle.

The fact that the Option 30 MEMORY test ran with no errors indicated the Diagnostic ROM was able to communicate with the Option 30 8x300 coprocessor and successfully read/modify/write the Option 30 32KB of RAM.

This communication uses the PIAs on the I/O board to generate commands to the Option 30 and read the results from Option 30.

These same PIAs are used to control the Display and Vector boards to move and draw vectors including the vectors in text - so that hardware is also working - even when the Option 30 board is present.

The Option 30 Operators Manual including the Quick Reference Guide and Service Manual is located here:

https://w140.com/tekwiki/images/1/1c/070-2289-02.pdf

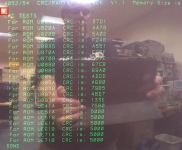

The next photo from the VintageTek museum shows using the Diagnostic ROM Pack to perform a ROM CRC test on the 4054A BASIC ROMs - which match my 4054A BASIC ROMs v1.5 (except for my MFM pack in the second slot so UE51A and UE51B show non-zero CRCs).

Note my screenshot on the right shows the blinking orange (Option 31 Color Dynamics CRT - which is installed in both computers), but the left image shows a orange dot - not blinking, and the VintageTek computer BUSY light is on and the computer is hung.

So the VintageTEK Option 30 issue appears to be associated with the blinking cursor.

Without Option 30 installed - the blinking orange cursor is displayed, which is done in BASIC ROM firmware.

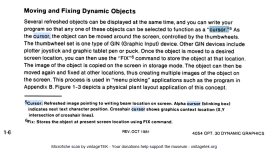

With Option 30 installed - the cursor is done by the Option 30 board and the cursor can be changed to any Option 30 object as indicated on this page of the Option 30 manual:

This Option 30 manual page indicates there are several different Option 30 object numbers can be used as the cursor, in addition to a user defined object number:

My suspicion is something is wrong with their Option 30 ability to blink the cursor.

I have burned a new set of Option 30 PROMs, tested them on my Option 30 and sent them to vintageTEK museum, but replacing the PROMs did NOT fix the cursor problem.

My Option 30 is working so I could capture logic analyzer data if that helps.

They have a logic analyzer and were looking at the PROM signals.

Does anyone have suggestions on our next step to repair their Option 30?

What works:

- Without the Option 30 board, their 4054A boots BASIC and run programs from a Flash Drive that I donated to the museum along with a Jos Dreesen Multifunction ROM Pack.

- With the Option 30 board installed and Jos Dressen's 4052/4054 Diagnostic ROM Pack installed and set to run the Option 30 RAM test, the test shows Option 30 RAM is OK

What fails:

- With the Option 30 board and Diagnostic ROM - after the Option 30 test (or any other Diag test), the 4054A is hung and does not return to BASIC and instead of a rectangular blinking cursor - they just get a dot where the cursor should be

The error message after the Option 30 MEMORY TEST is NOT a problem with the Option 30 MEMORY, it is listed in the 4052 Diagnostic ROM Pack manual page 18 as happening after the test if the 4054A only has 32KB of RAM:

What is an error in the Option 30 MEMORY test photo is the GREEN dot above the OPT 30 TESTS - this should be a blinking cursor rectangle.

The fact that the Option 30 MEMORY test ran with no errors indicated the Diagnostic ROM was able to communicate with the Option 30 8x300 coprocessor and successfully read/modify/write the Option 30 32KB of RAM.

This communication uses the PIAs on the I/O board to generate commands to the Option 30 and read the results from Option 30.

These same PIAs are used to control the Display and Vector boards to move and draw vectors including the vectors in text - so that hardware is also working - even when the Option 30 board is present.

The Option 30 Operators Manual including the Quick Reference Guide and Service Manual is located here:

https://w140.com/tekwiki/images/1/1c/070-2289-02.pdf

The next photo from the VintageTek museum shows using the Diagnostic ROM Pack to perform a ROM CRC test on the 4054A BASIC ROMs - which match my 4054A BASIC ROMs v1.5 (except for my MFM pack in the second slot so UE51A and UE51B show non-zero CRCs).

Note my screenshot on the right shows the blinking orange (Option 31 Color Dynamics CRT - which is installed in both computers), but the left image shows a orange dot - not blinking, and the VintageTek computer BUSY light is on and the computer is hung.

So the VintageTEK Option 30 issue appears to be associated with the blinking cursor.

Without Option 30 installed - the blinking orange cursor is displayed, which is done in BASIC ROM firmware.

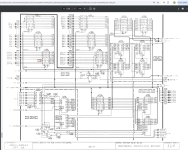

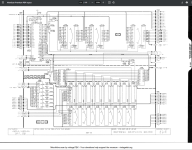

With Option 30 installed - the cursor is done by the Option 30 board and the cursor can be changed to any Option 30 object as indicated on this page of the Option 30 manual:

This Option 30 manual page indicates there are several different Option 30 object numbers can be used as the cursor, in addition to a user defined object number:

My suspicion is something is wrong with their Option 30 ability to blink the cursor.

I have burned a new set of Option 30 PROMs, tested them on my Option 30 and sent them to vintageTEK museum, but replacing the PROMs did NOT fix the cursor problem.

My Option 30 is working so I could capture logic analyzer data if that helps.

They have a logic analyzer and were looking at the PROM signals.

Does anyone have suggestions on our next step to repair their Option 30?

Last edited: