Hi Johann,

It's amazing you have come very far with your scipt, my compliments!

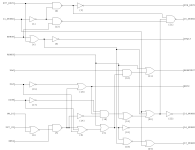

And let's not forget that your script is a one-step solution, including to do the work of Logic Friday as well.

That saves a lot more time in the reverse engineering process.

I was initially not even able to find concise clear instructions that I should use Logic Friday or similar after obtaining the PA.EXE output.

So your script is potentially able to save a lot of time and work!

It would be really great if you could arrive at the same results as mine in a single analysis, which would definitely validate the script in the use case example of U87.

I have done a careful compare for the terms in your output.

Code:

~END_CYC = Q4

# Q4;

| AIOW & ~RES_0WS

# AIOW & !RES_0WS

| RAS & ~RES_0WS

# RAS & !RES_0WS

| FSYS_16 & Q1 & RAS

FSYS_16 & Q1 & RAS

| AIOW & Q1 & ~IO_CS_16

# AIOW & !IO_CS_16 & Q1

| Q1 & ~IOR & ~IO_CS_16

# !IOR & !IO_CS_16 & Q1

DMA_AEN = AEN_1 & AEN_2

DMA_AEN = AEN_1 & AEN_2;

XA0 = 0

XA0 = 'b'0;

XA0.OE = ~AEN_2

XA0.oe = !AEN_2;

XBHE.OE = ~AEN_1 | ~AEN_2

!XBHE.oe = DMA_AEN;

(no value from your script)

RES_0WS.oe = 'b'0;

XBHE = AEN_2 & ~AEN_1 & ~XA0

XBHE = AEN_2 & !XA0;

~GATE_245 =

FSYS_16 & RAS & XA0 & ~AEN_1

# !AEN_1 & FSYS_16 & RAS & XA0

| FSYS_16 & RAS & ~AEN_1 & ~AEN_2

# !AEN_1 & !AEN_2 & FSYS_16 & RAS

| FSYS_16 & XA0 & ~AEN_1 & ~IOR

# !AEN_1 & FSYS_16 & !IOR & XA0;

| FSYS_16 & ~AEN_1 & ~AEN_2 & ~IOR

# !AEN_1 & !AEN_2 & FSYS_16 & !IOR

| AEN_1 & AEN_2 & AIOW & IO_CS_16 & XA0 & ~XBHE

AEN_1 & AEN_2 & AIOW & IO_CS_16 & XA0 & !XBHE

| AEN_1 & AEN_2 & IO_CS_16 & XA0 & ~IOR & ~XBHE

# AEN_1 & AEN_2 & !IOR & IO_CS_16 & XA0 & !XBHE

| AEN_1 & AEN_2 & RAS & XA0 & ~FSYS_16 & ~XBHE

# AEN_1 & AEN_2 & !FSYS_16 & RAS & XA0 & !XBHE

| AEN_1 & AEN_2 & XA0 & ~FSYS_16 & ~MEMW & ~XBHE

~DIR_245 = MEMW & RAS & ~AEN_1

!AEN_1 & MEMW & RAS

| AEN_1 & AEN_2 & AIOW & ~XBHE

# AEN_1 & AEN_2 & AIOW & !XBHE;

| AEN_1 & AEN_2 & ~MEMW & ~XBHE

# AEN_1 & AEN_2 & !MEMW & !XBHE

~DATA_CONV = AEN_1 & AEN_2 & AIOW & IO_CS_16 & Q1 & ~XA0 & ~XBHE

# AEN_1 & AEN_2 & AIOW & IO_CS_16 & Q1 & !XA0 & !XBHE;

| AEN_1 & AEN_2 & IO_CS_16 & Q1 & ~IOR & ~XA0 & ~XBHE

# AEN_1 & AEN_2 & !IOR & IO_CS_16 & Q1 & !XA0 & !XBHE

| AEN_1 & AEN_2 & Q1 & RAS & ~FSYS_16 & ~XA0 & ~XBHE

AEN_1 & AEN_2 & !FSYS_16 & Q1 & RAS & !XA0 & !XBHE

There are a few things which stand out, one of which I think can be easily solved with a small addition, so let's start with this one:

RES_0WS.oe = 'b'0;

Any input/output pin which is used exclusively as an input, and not switching to being an output under any circumstance, not having any OE equation, should have the OE function permanently disabled.

So if there is no value for PIN.oe determined by the analysis, and it's not appearing as an output in the analysis, in other words, if PIN appears as an input pin, having no OE function, the script should state the PIN.oe value to be 'b'0. It's important to state this to WinCupl otherwise it may assume wrongly that PIN.oe equals 'b'1. Maybe this is some kind of bug or something I am not seeing why WinCupl does this, so the safe path would be the above stating of PIN.oe = 'b'0 by the script.

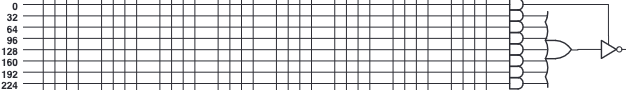

Using Logic Friday for !GATE_245 -only-, I was getting

Minimized:

GATE_245 =

RAS AEN_1' AEN_2' FSYS_16

+ IOR' AEN_1' AEN_2' FSYS_16

+ RAS AEN_1' FSYS_16 XA0

+ IOR' AEN_1' FSYS_16 XA0

+ IOR' IO_CS_16 AEN_1 AEN_2 XA0 XBHE'

+ AIOW IO_CS_16 AEN_1 AEN_2 XA0 XBHE'

+ RAS AEN_1 AEN_2 FSYS_16' XA0 XBHE'

+ MEMW' AEN_1 AEN_2 FSYS_16' XA0 XBHE'

The last term here can be reduced by the following reasoning:

RAS from the circuit diagram of the 5170 is a positive logic combination of !MEMW and !MEMR.

!RAS = !MEMW & !MEMR

Which means that RAS is positive logic true if !MEMW is negative logic true OR !MEMR is negative logic true.

So from this, being an OR function, it could be reasoned that

+ MEMW' AEN_1 AEN_2 FSYS_16' XA0 XBHE'

is covered by

+ RAS AEN_1 AEN_2 FSYS_16' XA0 XBHE'

and thus the term with !MEMW can be removed from the product terms by reasoning only of the person looking at the matter.

Of course, in this case, both PA.EXE and your script resulted in the same terms so no difference here.

The number of product terms per output which can be compiled in WinCupl is a maximum of 7 AND-OR terms.

Having more terms is technically not an error, only a problem for the person trying to make a functional GAL.

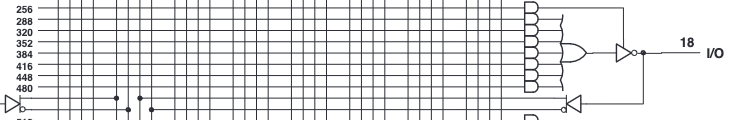

XBHE.OE = ~AEN_1 | ~AEN_2

!XBHE.oe = DMA_AEN;

Here we see that by rewriting

XBHE.OE = !AEN_1 + !AEN_2

-> !XBHE.OE = AEN_1 & AEN_2

-> !XBHE.OE = DMA_AEN

Which is using output DMA_AEN as the inverse OE function, which WinCupl only seemed to be willing to accept for achieving a successful compile.

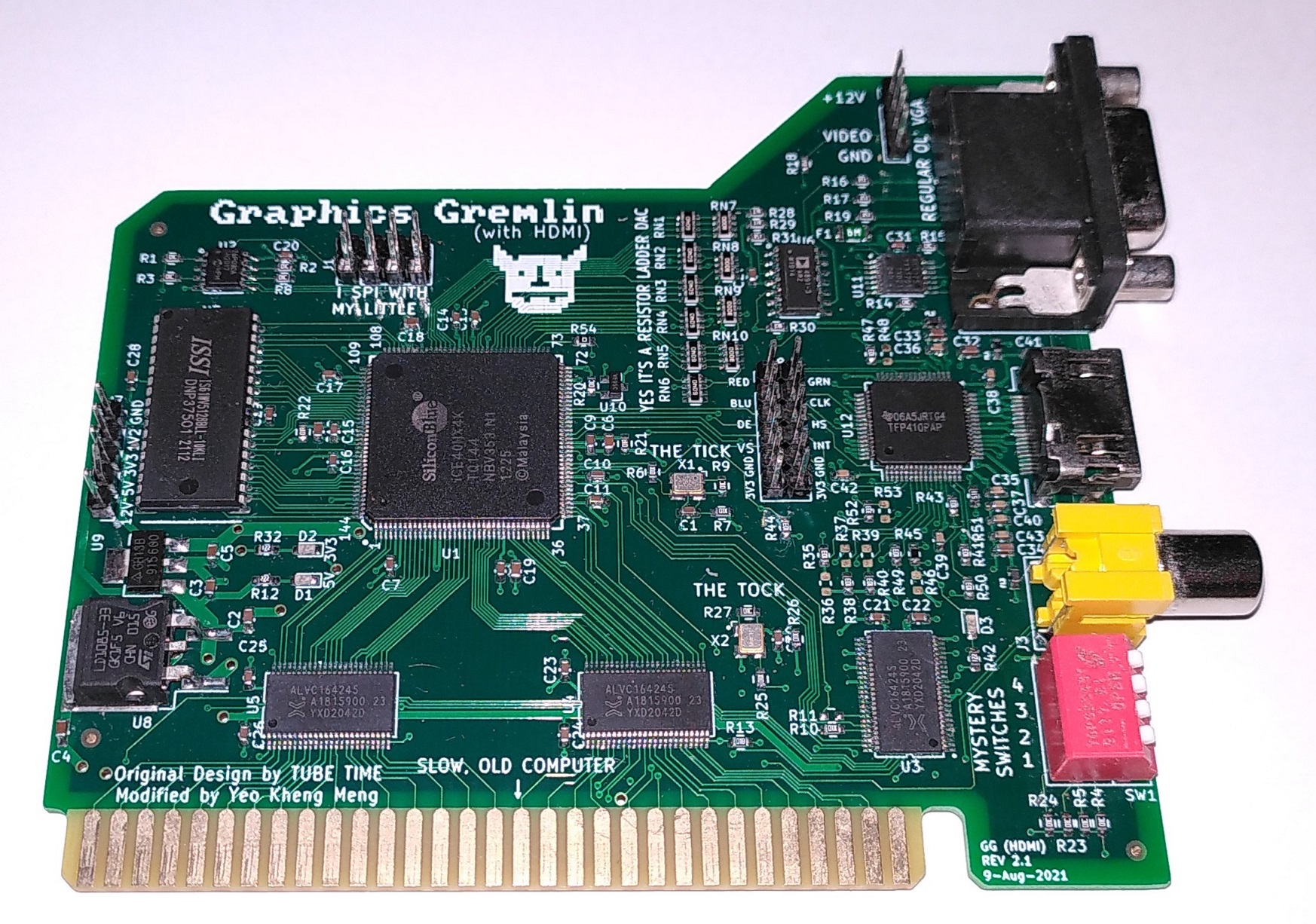

I have done a final evaluation of my work to see where the problem was created. The biggest problem during my testing work was that I was thrown off by the fact that XA0 and XBHE were being used as both an input and output. Which at first appeared to be impossible and conflicting information, leading me to dismiss it at first, however looking at it again later, it made sense after all because during DMA the CPU is inactive, leaving XA0 and XBHE as tri-state.

That was the seemingly smallest thing which turned out to be the biggest problem in testing.

None of the test GALs could function if the XA0 and XBHE output and .oe functions were not present because these prevented DMA from functioning at all.

So this point was preventing any of my tests with the GAL to work at all, resulting in a totally "dead" 5170 when testing.

Only when connecting U87 and my GAL to the same inputs, by coincidence, I finally discovered the real problem with XA0 and XBHE because having U87 connected with none of the 5 outputs wired to the 5170, I was getting a functional mainboard. That was the final clue that something strange must be going on with one of the inputs being an output in certain conditions.

And these missing output and OE equations for XA0 and XBHE resulted in the deviating results with the EPROM compare reads as well.

Which I then attempted to explain with your other script into additional output terms for !GATE_245 for those reads.

I then reduced these away with reasoning those additional output terms to be covered by a few other existing equations.

So that was a seeming contradiction as well, for which the real explanation were of course the output and .oe terms for XBHE and XA0.

So here also my total lack of PAL reverse engineering experience, which I readily admit, literally it was my first time, played a big role to let me doubt the information from PA.EXE at first. I also had not done any work with PA.EXE before and was yet to gain confidence in it in my personal practical experience. A few times I had the thought that I should contact someone with more experience to discuss the problem. Maybe that would have saved me a lot of time.

One final difference I noticed is this:

your python script outputs:

XBHE = AEN_2 & ~AEN_1 & ~XA0

PA.EXE outputs:

XBHE = AEN_2 & !XA0;

I am wondering how this different answer can appear, I can't explain it and it must be some difference in the software.

I can't by any reasoning assume that the AND term ~AEN_1 can be excluded to be always valid.

So it's unclear to me.

PA.EXE outputs literally:

!XBHE = !AEN_2 & !XA0

# !AEN_2 & XA0

# AEN_2 & XA0;

Where !AEN_1 is eliminated by PA.EXE and not appearing at all.

If you could find this problem that would be really great Johann!

And a small thing, would it be possible to rewrite the outputs using "#" or even "+" instead of "|", and using "!" instead of "~" ?

If possible, that would look even better!

Anyway, I must pay you a big compliment Johann, your python skill in this practical application is impressive!

And I just want to say it clearly once more, my only concern, in both my work and this thread, is to fully preserve and recreate the 5170 in my own modern recreation.

I was totally surprised to find that there was no definitive logic for U87 available on the entire internet.

This matter has cost me around three weeks of time in total.

But the value I did get out of it was a gain of experience that I developed from it.

Which arguably is another reason for me to do these projects, other than it being simply cool!

I feel sorry for the IBM team that they were not credited so much for their amazing work on the 5170 after getting famous for creating the PC and XT models. I mean, the 5170 was really a big milestone and iconic! Their "secret sauce"-alike solutions for true 8 bit software and hardware compatibility was absolutely genius and elemental in pushing the industry standard of PCs forward into 16 bit technology in a totally acceptable and "painless" way for anyone looking at the new technology! This point deserves proper credit and should never be overlooked!

When I search for the 5170 development, I hardly see the names of Bill Lowe and Don Estridge mentioned at all. If anyone here reading this knows of a documentary or any other material about the 5170 project, I would really appreciate a mention here! I am really interested in the historical aspect as well, not only the technology.