Harry,

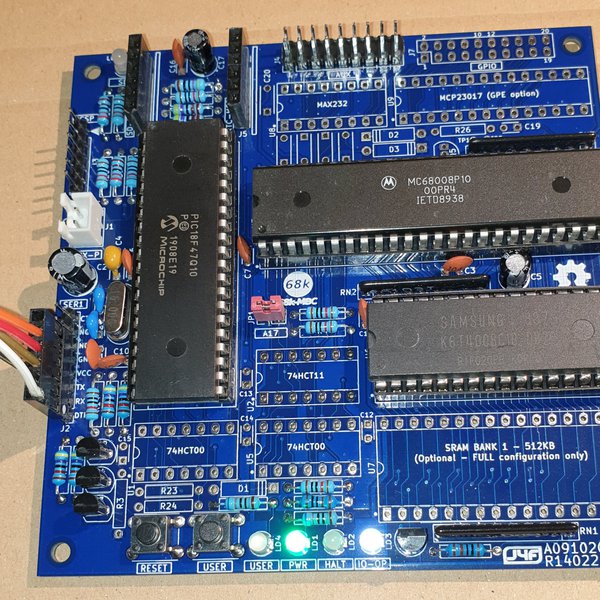

S100 is enormous amount of board space! How do you feel about CPLD in board designs? CPLD saves lots of board space so what you want can be done in 2"x4" pc board if CPLD is involved. For 68000, the idea is eliminating 2 EPROM and use x16 DRAM and bootstrap from CF disk. So the core design is 3 chips (68000, DRAM, CPLD) + CF disk. A DUART can be added to the core design. It can be something like

T68KRC (3"x4"), but smaller because the serial bootstrap EEPROM is replaced with existing CF disk.

Bill

PS, if you accept serial bootstrapping, then CPLD and DRAM can fit inside the footprint of DIP64 68000, so the core design is not bigger than DIP64 68000.

PPS, another small design is based on P90CE201 which is derived from 68008.

Kuno fits in Arduino Mega enclosure.