80186 Enthusiast

Experienced Member

- Joined

- May 18, 2023

- Messages

- 53

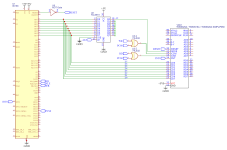

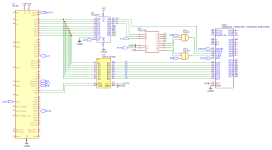

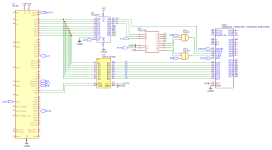

Here's a schematic I've made for an address decoder for a TMS9918A Video Display Processor. In this Post, I'll go over how this Address Decoder Works .

I've based this address decoder off of schematics in the Datasheet (I'll put those schematics at the bottom of this post) for the TMS9918A. The main component of this Address Decoder is a 47LS138 Decoder/ Demultiplexer IC.

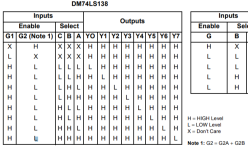

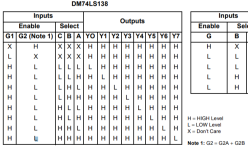

The I have Enable Pin G1 tied to 5v, and Enable Pin G2A tied to GND. Enable Pin G2B is connected to CPU pin PCS0. PSC0 is used to put the VDP on the CPU's memory Map, this signal will be programmed to be pulled low whenever the CPU needs to communicate with the VDP. (74LS138 truth table below)

The VDP requires specific addresses (or ports as the VDP datasheet says) to let it know when the CPU is Writing, Writing an Address, reading from VRAM and Reading the VDP Status Register. So I referenced the Datasheet for what Ports I wanted to use and which address pins I needed to use. So I converted each Port/ Addresses I needed to use and created the following table:

So I need Address Pins A15, A2 and A1. By using those Address Pins as the Select Input pins in the 74LS138 in the following order:

That's it for this post, as always, any help and advice will be thanked and appreciated in Advance! Here are are the schematics from the Datasheet as I mentioned earlier in this Post!

I've based this address decoder off of schematics in the Datasheet (I'll put those schematics at the bottom of this post) for the TMS9918A. The main component of this Address Decoder is a 47LS138 Decoder/ Demultiplexer IC.

The I have Enable Pin G1 tied to 5v, and Enable Pin G2A tied to GND. Enable Pin G2B is connected to CPU pin PCS0. PSC0 is used to put the VDP on the CPU's memory Map, this signal will be programmed to be pulled low whenever the CPU needs to communicate with the VDP. (74LS138 truth table below)

The VDP requires specific addresses (or ports as the VDP datasheet says) to let it know when the CPU is Writing, Writing an Address, reading from VRAM and Reading the VDP Status Register. So I referenced the Datasheet for what Ports I wanted to use and which address pins I needed to use. So I converted each Port/ Addresses I needed to use and created the following table:

A19 A18 A17 A16 | A15 A14 A13 A12 | A11 A10 A9 A8 | A7 A6 A5 A4 | A3 A2 A1 A0 | |

0 0 0 0 | 1 0 0 0 | 0 0 0 0 | 0 0 0 0 | 0 0 0 0 | 0x08000: Write Data to VRAM |

0 0 0 0 | 1 0 0 0 | 0 0 0 0 | 0 0 0 0 | 0 0 1 0 | 0x08002: Write Address to VRAM |

0 0 0 0 | 1 0 0 0 | 0 0 0 0 | 0 0 0 0 | 0 1 0 0 | 0x08004: Read Data from VRAM |

0 0 0 0 | 1 0 0 0 | 0 0 0 0 | 0 0 0 0 | 0 1 1 0 | 0x08006: Read VDP Status |

So I need Address Pins A15, A2 and A1. By using those Address Pins as the Select Input pins in the 74LS138 in the following order:

- A15 => C

- A2 => B

- A1 => A

- Y4 low = Write Data to VRAM (A15 High: 0x08000)

- Y5 low = Write Address to VRAM (A15, A1 High: 0x08002)

- Y6 low = Read Data from VRAM (A15, A2 High: 0x08004)

- Y7 low = Read VDP Status Register (A15, A2, A1 High: 0x08006)

That's it for this post, as always, any help and advice will be thanked and appreciated in Advance! Here are are the schematics from the Datasheet as I mentioned earlier in this Post!