Upcoming Events:

- VCF South West - June 14 - 16, Davidson-Gundy Alumni Center at University of Texas at Dallas

- VCF West - Aug 2 - 3, Computer History Museum, Mountain View, CA

- VCF Midwest - Sept 7 - 8 2024, Schaumburg, IL

- VCF SoCal - Mid February 2025, Location TBD, Southern CA

- VCF East - April 2025, Infoage Museum, Wall NJ

-

Please review our updated Terms and Rules here

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Any .LIB for NEC V20 with ASM86.COM or ASM86.CMD?

- Thread starter Just4Fun

- Start date

Chuck(G)

25k Member

As far as I'm aware, if you're talking the 8080-compatible mode, the instruction set is identical to the 8080--no extra codes.

As far as I'm aware, if you're talking the 8080-compatible mode, the instruction set is identical to the 8080--no extra codes.

The question was about ASM86 though. Not sure if anyone else has done this (and tested it properly), but here's my version:

Code:

;;;;;

;;;;; 186 and NEC instructions for ASM86

;;;;;

;;;

;;; 186 instruction set

;;;

CodeMacro pusha

db 60h

EndM

CodeMacro popa

db 61h

EndM

CodeMacro bound reg:Rw,mem:Mw

segfix mem

db 62h

modrm reg,mem

EndM

CodeMacro push imm:Dw

db 68h

dw imm

EndM

CodeMacro imul dst:Rw,src:Ew,mpy:Dw

segfix src

db 69h

modrm dst,src

dw mpy

EndM

CodeMacro push imm:Dsb

db 6ah

db imm

EndM

CodeMacro imul dst:Rw,src:Ew,mpy:Dsb

segfix src

db 6bh

modrm dst,src

db mpy

EndM

CodeMacro insb

db 6ch

EndM

CodeMacro insw

db 6dh

EndM

CodeMacro outsb

db 6eh

EndM

CodeMacro outsw

db 6fh

EndM

CodeMacro outs port:Rw(DX),src:Eb

segfix src

db 6eh

EndM

CodeMacro outs port:Rw(DX),src:Ew

segfix src

db 6fh

EndM

CodeMacro rol dst:Eb,cnt:Db

segfix dst

db 0c0h

modrm 0,dst

db cnt

EndM

CodeMacro ror dst:Eb,cnt:Db

segfix dst

db 0c0h

modrm 1,dst

db cnt

EndM

CodeMacro rcl dst:Eb,cnt:Db

segfix dst

db 0c0h

modrm 2,dst

db cnt

EndM

CodeMacro rcr dst:Eb,cnt:Db

segfix dst

db 0c0h

modrm 3,dst

db cnt

EndM

CodeMacro shl186 dst:Eb,cnt:Db

segfix dst

db 0c0h

modrm 4,dst

db cnt

EndM

CodeMacro shr186 dst:Eb,cnt:Db

segfix dst

db 0c0h

modrm 5,dst

db cnt

EndM

CodeMacro sar dst:Eb,cnt:Db

segfix dst

db 0c0h

modrm 7,dst

db cnt

EndM

CodeMacro rol dst:Ew,cnt:Db

segfix dst

db 0c1h

modrm 0,dst

db cnt

EndM

CodeMacro ror dst:Ew,cnt:Db

segfix dst

db 0c1h

modrm 1,dst

db cnt

EndM

CodeMacro rcl dst:Ew,cnt:Db

segfix dst

db 0c1h

modrm 2,dst

db cnt

EndM

CodeMacro rcr dst:Ew,cnt:Db

segfix dst

db 0c1h

modrm 3,dst

db cnt

EndM

CodeMacro shl186 dst:Ew,cnt:Db

segfix dst

db 0c1h

modrm 4,dst

db cnt

EndM

CodeMacro shr186 dst:Ew,cnt:Db

segfix dst

db 0c1h

modrm 5,dst

db cnt

EndM

CodeMacro sar dst:Ew,cnt:Db

segfix dst

db 0c1h

modrm 7,dst

db cnt

EndM

CodeMacro enter siz:D,lev:Db

db 0c8h

dw siz

db lev

EndM

CodeMacro leave

db 0c9h

EndM

;;; Workaround:

;;; Code macro names of "SHL" and "SHR" conflict with operators

;;; This problem does not occur with equates to already defined macro

;shl equ shl186

;shr equ shr186

;;;

;;; NEC Vxx instruction set

;;;

CodeMacro test1 dst:Eb,bit:Rb(CL)

segfix dst

db 0fh

db 10h

modrm 0,dst

EndM

CodeMacro test1 dst:Ew,bit:Rb(CL)

segfix dst

db 0fh

db 11h

modrm 0,dst

EndM

CodeMacro test1 dst:Eb,bit:Db(0,7)

segfix dst

db 0fh

db 18h

modrm 0,dst

db bit

EndM

CodeMacro test1 dst:Ew,bit:Db(0,15)

segfix dst

db 0fh

db 19h

modrm 0,dst

db bit

EndM

CodeMacro clr1 dst:Eb,bit:Rb(CL)

segfix dst

db 0fh

db 12h

modrm 0,dst

EndM

CodeMacro clr1 dst:Ew,bit:Rb(CL)

segfix dst

db 0fh

db 13h

modrm 0,dst

EndM

CodeMacro clr1 dst:Eb,bit:Db(0,7)

segfix dst

db 0fh

db 1ah

modrm 0,dst

db bit

EndM

CodeMacro clr1 dst:Ew,bit:Db(0,15)

segfix dst

db 0fh

db 1bh

modrm 0,dst

db bit

EndM

CodeMacro set1 dst:Eb,bit:Rb(CL)

segfix dst

db 0fh

db 14h

modrm 0,dst

EndM

CodeMacro set1 dst:Ew,bit:Rb(CL)

segfix dst

db 0fh

db 15h

modrm 0,dst

EndM

CodeMacro set1 dst:Eb,bit:Db(0,7)

segfix dst

db 0fh

db 1ch

modrm 0,dst

db bit

EndM

CodeMacro set1 dst:Ew,bit:Db(0,15)

segfix dst

db 0fh

db 1dh

modrm 0,dst

db bit

EndM

CodeMacro not1 dst:Eb,bit:Rb(CL)

segfix dst

db 0fh

db 16h

modrm 0,dst

EndM

CodeMacro not1 dst:Ew,bit:Rb(CL)

segfix dst

db 0fh

db 17h

modrm 0,dst

EndM

CodeMacro not1 dst:Eb,bit:Db(0,7)

segfix dst

db 0fh

db 1eh

modrm 0,dst

db bit

EndM

CodeMacro not1 dst:Ew,bit:Db(0,15)

segfix dst

db 0fh

db 1fh

modrm 0,dst

db bit

EndM

CodeMacro add4s

db 0fh

db 20h

EndM

CodeMacro add4s dst:Eb,src:Eb

nosegfix es,dst

segfix src

db 0fh

db 20h

EndM

CodeMacro sub4s

db 0fh

db 22h

EndM

CodeMacro sub4s dst:Eb,src:Eb

nosegfix es,dst

segfix src

db 0fh

db 22h

EndM

CodeMacro cmp4s

db 0fh

db 26h

EndM

CodeMacro cmp4s dst:Eb,src:Eb

nosegfix es,dst

segfix src

db 0fh

db 26h

EndM

CodeMacro rol4 dst:Eb

segfix dst

db 0fh

db 28h

modrm 0,dst

EndM

CodeMacro ror4 dst:Eb

segfix dst

db 0fh

db 2ah

modrm 0,dst

EndM

CodeMacro ins dst:Rb,src:Rb

db 0fh

db 31h

modrm src,dst

EndM

CodeMacro ins dst:Rb,src:Db(0,15)

db 0fh

db 39h

modrm 0,dst

db src

EndM

CodeMacro ext dst:Rb,src:Rb

db 0fh

db 33h

modrm src,dst

EndM

CodeMacro ext dst:Rb,src:Db(0,15)

db 0fh

db 3bh

modrm 0,dst

db src

EndM

CodeMacro brkem vec:Db

db 0fh

db 0ffh

db vec

EndM

CodeMacro repnc

db 64h

EndM

CodeMacro repc

db 65h

EndM

;;; only in 8080 emulation mode:

CodeMacro calln vec:Db

db 0edh

db 0edh

db vec

EndM

CodeMacro retem

db 0edh

db 0fdh

EndMI had done the 186 opcodes before, so these should work at least. NEC-specific ones were implemented about an hour ago, so there may be some mistakes.

edit: Commented out "workaround" since the old SHL and SHR would be overriden, and the macros only implement the immediate variant. Use SHL186 and SHR186 for the shift-immediate instructions.

edit2: added CALLN and RETEM in case you want to emulate CP/M-80

Last edited:

Chuck(G)

25k Member

Oh, I see--the Z80.LIB thing had me confused.

I may have a library from NEC Natick somewhere in my collection. The problem is that NEC relabeled everying, right down to the registers and x86 opcodes, so a "real" NEC implementation may not be particularly desirable.

I may have a library from NEC Natick somewhere in my collection. The problem is that NEC relabeled everying, right down to the registers and x86 opcodes, so a "real" NEC implementation may not be particularly desirable.

The question was about ASM86 though...

@dreNorteR: Thanks very much!!! It is exactly what I was looking for... (and with the 8080 emulation instructions too...) :D

@ Chuck(G): Yes, the "renaming" of CPU pins and instructions is terrible... Sadly because NEC documentation IMHO is very well written...

BTW: I've almost done the the boot procedure and the core I/O read/write and interrupt "emulation" too (both pushed/emulated by the STM32F030R8 ), so its almost time to do some assembler coding...

(the address of the first instruction in the video is FFFF:0000 and not FFFF:00F0, damned x86 segments...

Chuck(G)

25k Member

One thing that stopped me from using the non-186 V-series instruction additions was that, once you use them, you're locked in to the V-series hardware. Not something you want in software you write. The performance improvement gained by using those V-unique instructions is usually pretty small, so not worth it, at least for me. If you use the 186 additions only, at least your code will run on a 186/286+ system in addition to the V-series stuff.

That being said, a simple web search turns up a few macro libraries with V-series instructions. There's even an assembler or two that have an absolutely blank instruction set--the processor is defined by a series of tables contained on files. That was the way the original ISIS-II x86 assembler was--startup time on a floppy-based system was terrible because the assembler had to read a file of opdefs.

That being said, a simple web search turns up a few macro libraries with V-series instructions. There's even an assembler or two that have an absolutely blank instruction set--the processor is defined by a series of tables contained on files. That was the way the original ISIS-II x86 assembler was--startup time on a floppy-based system was terrible because the assembler had to read a file of opdefs.

Attachments

Last edited:

I haven't analyzed that in detail yet, but I thing that the "limiting factor" is the lack of a video card.

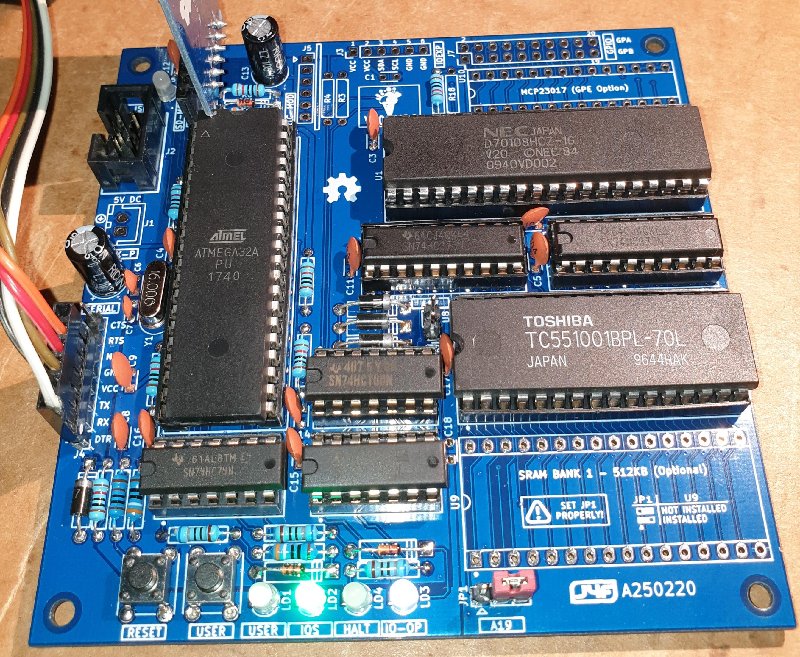

The V20-MBC has all the address space (1024KB) fitted with RAM, so the RAM isn't a problem.

Using a custom BIOS probably it should be possible to run MSDOS with restrictions due to the lack of a video card, so only "text programs" could run here (using only BIOS calls).

This means that the custom BIOS should "remap" the ASCII video I/O on the serial port (using VT100-like cursor control).

The "Virtual I/O engine" on the Atmega32 can handle IRQ on the V20 bus without limitations, so no problem to emulate i.e. a keyboard IRQ (I've already tested on the breadboard prototype the use of a keyboard/serial IRQ in the 8080 mode, using "mixed" 8088/8080 ISR routines...).

Currently I'm starting to deal with the CP/M-80 (for the 8080 mode) and CP/M-86 porting...

The V20-MBC has all the address space (1024KB) fitted with RAM, so the RAM isn't a problem.

Using a custom BIOS probably it should be possible to run MSDOS with restrictions due to the lack of a video card, so only "text programs" could run here (using only BIOS calls).

This means that the custom BIOS should "remap" the ASCII video I/O on the serial port (using VT100-like cursor control).

The "Virtual I/O engine" on the Atmega32 can handle IRQ on the V20 bus without limitations, so no problem to emulate i.e. a keyboard IRQ (I've already tested on the breadboard prototype the use of a keyboard/serial IRQ in the 8080 mode, using "mixed" 8088/8080 ISR routines...).

Currently I'm starting to deal with the CP/M-80 (for the 8080 mode) and CP/M-86 porting...