daver2

10k Member

I have checked myself, and the firmware for UD9 that has been burnt looks correct to me also.

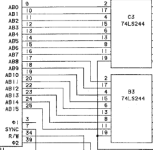

Based on that we are looking at the CPU -> ADDRESS BUFFERS -> ROM (UD9) -> DATA BUS -> CPU interface, along with the UD9 address decoding - and any potential bus contention.

Assuming the CPU address bus through the address bus buffers to the UD9 ROM has been checked out - then these should be OK.

The data bus from the ROMs goes straight back to the CPU. With the two PIAs and VIA removed, these should be out of the equation. The only other devices that could cause data bus contention would be buffers E9 and E10. There is some logic on schematic sheet 1 that controls the direction of these buffers - so that could be faulty (or one/both of E9/E10). In this instance, I would expect to see evidence of bus contention on the data bus.

It would be good if we could see initial signs of activity on UD9 pin 20 immediately following a reset to demonstrate that the CPU is trying to read the restart vector from the ROM.

I am not sure whether we have any other ROMs in place (other than my test firmware in UD9). If so, perhaps better to remove them. I have seen a faulty ROM disturb the data bus before now.

That is my "train of thought" for what it's worth. Enjoy!

Enjoy.

Dave

Based on that we are looking at the CPU -> ADDRESS BUFFERS -> ROM (UD9) -> DATA BUS -> CPU interface, along with the UD9 address decoding - and any potential bus contention.

Assuming the CPU address bus through the address bus buffers to the UD9 ROM has been checked out - then these should be OK.

The data bus from the ROMs goes straight back to the CPU. With the two PIAs and VIA removed, these should be out of the equation. The only other devices that could cause data bus contention would be buffers E9 and E10. There is some logic on schematic sheet 1 that controls the direction of these buffers - so that could be faulty (or one/both of E9/E10). In this instance, I would expect to see evidence of bus contention on the data bus.

It would be good if we could see initial signs of activity on UD9 pin 20 immediately following a reset to demonstrate that the CPU is trying to read the restart vector from the ROM.

I am not sure whether we have any other ROMs in place (other than my test firmware in UD9). If so, perhaps better to remove them. I have seen a faulty ROM disturb the data bus before now.

That is my "train of thought" for what it's worth. Enjoy!

Enjoy.

Dave