daver2

10k Member

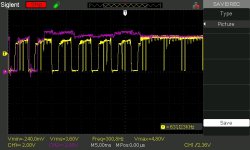

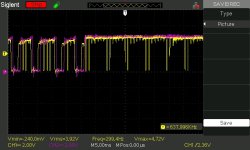

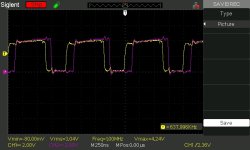

The simplest way to use the NOP generator is in conjunction with an oscilloscope.

Address line A0 from the CPU should be oscillating at 250 kHz. Address line A1 from the CPU should be oscillating at half that frequency (125 kHz) and so on down to address line A15.

The same should be true on the 'other side' of the '244 address buffers.

In fact, you should be able to check the address lines are functioning correctly all the way to the ROMs and the DRAM address multiplexers using this technique. Check the two ROMs at the extremes of the block of ROM devices (it has been known for tracks to fail partway along). If the ROMs are in sockets (yours probably are not) it is prudent to check all of the ROM device address lines (just in case of an IC socket fault). Laborious, but it does identify the issue (in the case of an address pin of course)

You can also check the '154 4:16 address decoder. But more of that later if these tests checkout OK.

Of course, if the previous post works OK, you can rule out the ROMs and we can concentrate on the DRAM address multiplexers.

I am on holiday at the moment, so only limited access to schematics and other documentation...

I will have a look at your PETTESTER RAM fault displays when I get back from my (long) walk...

Dave

Address line A0 from the CPU should be oscillating at 250 kHz. Address line A1 from the CPU should be oscillating at half that frequency (125 kHz) and so on down to address line A15.

The same should be true on the 'other side' of the '244 address buffers.

In fact, you should be able to check the address lines are functioning correctly all the way to the ROMs and the DRAM address multiplexers using this technique. Check the two ROMs at the extremes of the block of ROM devices (it has been known for tracks to fail partway along). If the ROMs are in sockets (yours probably are not) it is prudent to check all of the ROM device address lines (just in case of an IC socket fault). Laborious, but it does identify the issue (in the case of an address pin of course)

You can also check the '154 4:16 address decoder. But more of that later if these tests checkout OK.

Of course, if the previous post works OK, you can rule out the ROMs and we can concentrate on the DRAM address multiplexers.

I am on holiday at the moment, so only limited access to schematics and other documentation...

I will have a look at your PETTESTER RAM fault displays when I get back from my (long) walk...

Dave

Last edited: