ZoomPicard

New Member

- Joined

- Jan 10, 2019

- Messages

- 2

I have put together what I think are the correct components for this build:

https://www.mouser.com/ProjectManager/ProjectDetail.aspx?AccessID=1d22359016

At this point I can't confirm that these are all 100% correct, just my first stab at it. If anyone has any comments let me know

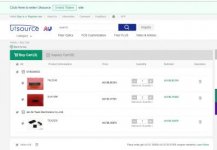

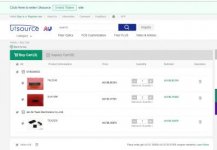

There are three parts I am ordering from UTSource. Sadly direct from UTSource they will only sell TEA2025 in packs of 10 so I am trying to buy from an alternative on that site (See Screenshot)

I will report on my progress once everything has arrived and I have put the board together

Product Cost total including the PCB which I got from Ebay here:

https://www.ebay.com.au/itm/PCB-MUS1099-ISA-8-bit-sound-card/382704656883

Is around $103 AUS ($73 USD) for myself living in Australia. I am sure US based it would around $50-70 USD

https://www.mouser.com/ProjectManager/ProjectDetail.aspx?AccessID=1d22359016

At this point I can't confirm that these are all 100% correct, just my first stab at it. If anyone has any comments let me know

There are three parts I am ordering from UTSource. Sadly direct from UTSource they will only sell TEA2025 in packs of 10 so I am trying to buy from an alternative on that site (See Screenshot)

I will report on my progress once everything has arrived and I have put the board together

Product Cost total including the PCB which I got from Ebay here:

https://www.ebay.com.au/itm/PCB-MUS1099-ISA-8-bit-sound-card/382704656883

Is around $103 AUS ($73 USD) for myself living in Australia. I am sure US based it would around $50-70 USD