Acquired a 8032-SK that spend many years in a barn in a coastal city. This has caused a fair amount of corrosion on the IC pins that are socketed, to the point that many of the pins literally fall off. This is on top of the hornets nest inside the machine!

First order of the day was to remove the built-in bomb but, after doing that, no joy in booting it up. Did a few things:

1. I replaced the CPU and Character ROM that both lost pins (the pins literally fell off!) but the machine does not start.

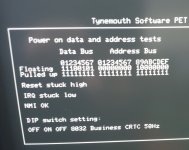

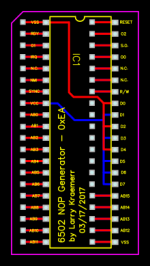

2. Installing one of Dave's (from Tynemouth) RAM/ROM replacement cards, and mapping everything out, gives the startup beeps but no display.

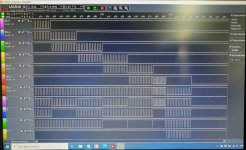

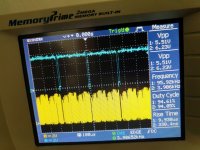

3. Looking at the video output signals, on the header connecting the monitor, I get H-sync but no V-Sync nor Video.

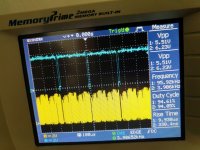

4. The RAM/ROM replacement card has a copy of (other) Dave's PETTESTER in it and if I select that, I get H-Sync and Video output but still no V-Sync.

5. I see the 7486 XOR that drives the video connector is socketed, so it looks like someone's worked on it before. Checking the input to the V-Sync XOR gate, shows no activity. So it seems the CRTC is not generating a V-Sync signal.

Any idea where to look next? Seems either the CRTC is not being set up or it's faulty?

Not a bad looking 8032-SK, taking into account it was in a barn for decades.

Think the drivers that must operate the chips, all left.....

Universal board with a Tynemouth board installed, allowing it to boot - but no display.

Getting H-Sync (blue) and Video (yellow). This is with PETTESTER. Normal bootup gives H-Sync but nothing else.

First order of the day was to remove the built-in bomb but, after doing that, no joy in booting it up. Did a few things:

1. I replaced the CPU and Character ROM that both lost pins (the pins literally fell off!) but the machine does not start.

2. Installing one of Dave's (from Tynemouth) RAM/ROM replacement cards, and mapping everything out, gives the startup beeps but no display.

3. Looking at the video output signals, on the header connecting the monitor, I get H-sync but no V-Sync nor Video.

4. The RAM/ROM replacement card has a copy of (other) Dave's PETTESTER in it and if I select that, I get H-Sync and Video output but still no V-Sync.

5. I see the 7486 XOR that drives the video connector is socketed, so it looks like someone's worked on it before. Checking the input to the V-Sync XOR gate, shows no activity. So it seems the CRTC is not generating a V-Sync signal.

Any idea where to look next? Seems either the CRTC is not being set up or it's faulty?

Not a bad looking 8032-SK, taking into account it was in a barn for decades.

Think the drivers that must operate the chips, all left.....

Universal board with a Tynemouth board installed, allowing it to boot - but no display.

Getting H-Sync (blue) and Video (yellow). This is with PETTESTER. Normal bootup gives H-Sync but nothing else.