voidstar78

Veteran Member

So, this is similar to my System/360 thread.

But System/3 appears to be a little more obscure. My understanding is the main feature of System/3 was the RPG II programming language. I'm not at all familiar with that, but I suspect many people maybe didn't code in raw machine code on System/3 - so in general less people may be familiar with its instruction set? Also like the S360 problem, there were a variety of S/3 Models. Something has led me to believe I'm dealing with Model 6 code here, but I'm not 100% certain.

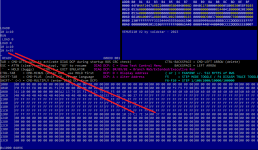

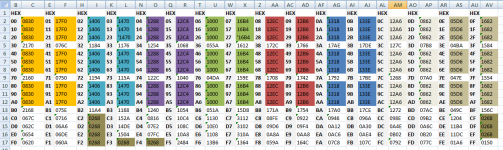

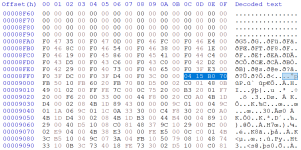

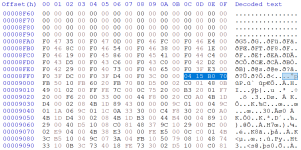

Here is the sample of the binary stream, which should be some System/3 machine code:

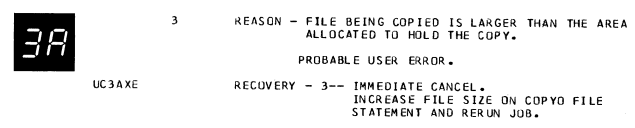

The classic challenge here is we don't know what sections are Data vs Code. One thing I noticed here is that each "section" of code (content separated by "islands" of empty 00 space), they all start with "F0 xx xx 00 F0 xx xx 00 F0 xx xx 00" and so on. Something runs in my mind is that the System/3 did have an "error code" display - and you could HALT the system and show two codes (on an LED or some part of the system). Can't recall where I read that, somewhere in here probably (site also has an inventory of remaining 1401 and S3's): http://www.ibmsystem3.nl/

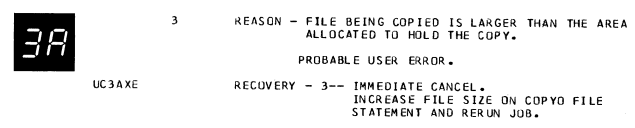

In that case, it could mean these "F0" sequences are kind of Data - in that they are offset addresses to use when certain error conditions happen (then Halt the system and display). Here is an example of what the LED looked like:

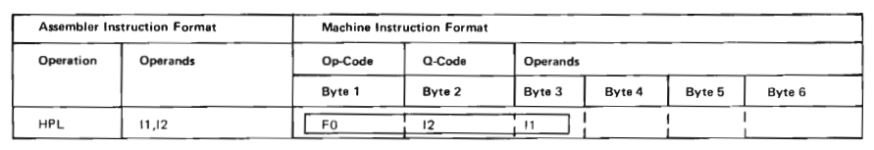

Here's what I'm using as the assembly reference:

I recall reading the System/3 is "famous" for not having any actual registers - it has a "base-register displacement addressing", but it's still in-memory.

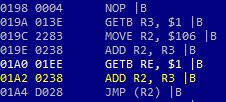

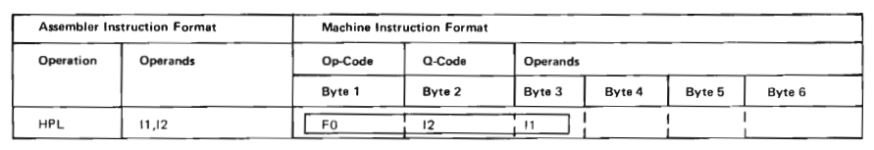

Which this is what it says about the F0 opcode instruction (pg68): (i.e. it should be 3-bytes, so what is the "00" doing in between the F0's in the sample above? maybe just a separate to make it easier to read, since HPL is going to halt the system anyway)

Halt Program Level

Starting at 0x8F80

Still not sure where the code starts after that.

But System/3 appears to be a little more obscure. My understanding is the main feature of System/3 was the RPG II programming language. I'm not at all familiar with that, but I suspect many people maybe didn't code in raw machine code on System/3 - so in general less people may be familiar with its instruction set? Also like the S360 problem, there were a variety of S/3 Models. Something has led me to believe I'm dealing with Model 6 code here, but I'm not 100% certain.

Here is the sample of the binary stream, which should be some System/3 machine code:

The classic challenge here is we don't know what sections are Data vs Code. One thing I noticed here is that each "section" of code (content separated by "islands" of empty 00 space), they all start with "F0 xx xx 00 F0 xx xx 00 F0 xx xx 00" and so on. Something runs in my mind is that the System/3 did have an "error code" display - and you could HALT the system and show two codes (on an LED or some part of the system). Can't recall where I read that, somewhere in here probably (site also has an inventory of remaining 1401 and S3's): http://www.ibmsystem3.nl/

In that case, it could mean these "F0" sequences are kind of Data - in that they are offset addresses to use when certain error conditions happen (then Halt the system and display). Here is an example of what the LED looked like:

Here's what I'm using as the assembly reference:

I recall reading the System/3 is "famous" for not having any actual registers - it has a "base-register displacement addressing", but it's still in-memory.

Which this is what it says about the F0 opcode instruction (pg68): (i.e. it should be 3-bytes, so what is the "00" doing in between the F0's in the sample above? maybe just a separate to make it easier to read, since HPL is going to halt the system anyway)

Halt Program Level

Starting at 0x8F80

Code:

F0 47 35 00 F0 47 0D 00 F0 46 FC 00 F0 46 E4 00

F0 46 8C 00 F0 46 54 00 F0 46 38 00 F0 46 1E 00

F0 46 19 00 F0 45 86 00 F0 45 41 00 F0 44 C4 00

F0 43 D5 00 F0 43 C6 00 F0 43 C0 00 F0 42 D2 00

F0 42 29 00 F0 40 73 00 F0 40 65 00 F0 3F E3 00

F0 3F DC 00 F0 3F D4 00 F0 3C 00 00 04 15 B0 70

FB 50 10 FB 60 20 FB 70 80 D5 00 02 C0 01 48 0B

49 01 02 00 FF FE 7C 00 0C 75 20 00 B3 20 01 F7

20 00 F6 20 00 33 00 00 44 F8 00 20 C0 A0 4B 1D

D4 00 02 08 4B 1D 89 43 00 00 00 9C 01 00 04 9C

01 1A 06 9C 01 1C 0A 33 30 00 C4 F8 30 20 C0 A0

4B 1D D4 30 02 08 4B 1D B3 00 44 B4 00 04 89 10

29 00 40 D5 10 08 C0 81 48 37 9C 10 29 00 BC 00

02 E9 04 00 4B 38 E3 00 00 FE E5 00 0C C0 01 4B

3C B5 10 04 9C 07 3A 04 FB 10 50 79 08 10 48 74

33 10 0B 3C 73 40 18 FE 73 30 02 D5 10 00 C0 81

48 6F FA 20 10 20 48 6F 6D 01 00 00 28 48 6F 78

08 14 48 6F B8 40 03 48 5F FE 7A 40 15 FE E5 00

1A C0 81 48 68 6D 01 1A 1A 28 48 6C F0 4B 34 FE

6D 10 29 29 20 4B 34 FE B8 10 10 4B 6C FE FB 10

30 FA 10 40 10 48 4C FE FB 10 50 B9 20 10 48 7D

78 04 10 48 7D FE 7B 80 10 FE 78 80 10 48 85 FE

B8 80 10 4B 38 FE BA 80 14 FE 78 40 10 48 8D FE

B8 40 10 4B 38 FE BA 40 14 FE 78 C0 10 48 93 FE

B8 80 11 4B 34 FE 33 30 00 45 F8 30 20 C0 A0 4BStill not sure where the code starts after that.