I’ve been staring at the Kaypro II video schematics tonight (the first version, without a controller) and it’s an clever design.

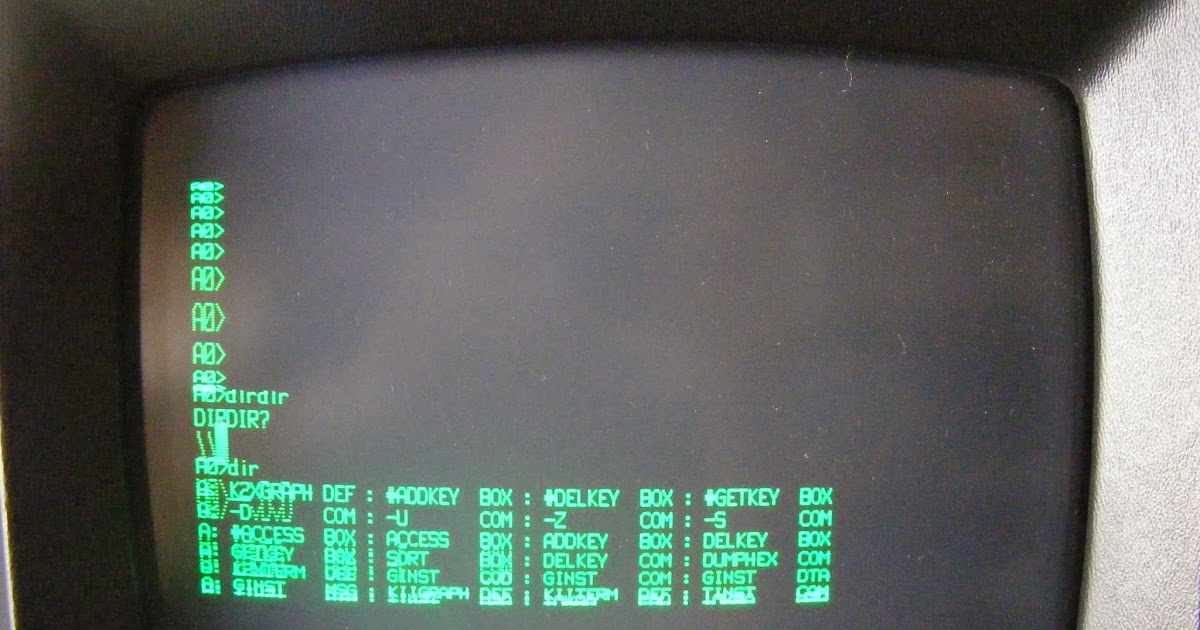

The video circuitry runs on its own clock, and no effort was made to synchronize memory access between the CPU and the video circuitry. It simply gives the CPU priority access to the VRAM. The video circuitry needs to read from VRAM every 7 pixels to fetch a row for a glyph out of the character generator ROM. If the CPU is busy accessing the VRAM when the video circuitry is trying to fetch those pixels, the video circuitry will read out black pixels.

What’s is clever is that this isn’t a big deal. Even if a scanline for a single character is missed, it’ll be drawn on the next frame, and was likely drawn in the previous frame, so the phosphor persistence on a display refreshing at 60 Hz will make the glitch barely noticeable. The video circuitry fetches from VRAM every 500 ns, much faster than the CPU’s theoretical maximum of a fetch or write every 3 µs. And a lot of the time the video circuitry is either vertical blanking, horizontal blanking, or doing blank lines between lines of text, so the chance of the CPU stepping on the video circuitry enough to cause noticeable glitching of the display is quite low.

Anyway, I thought it was a neat solution to the problem. It wasn’t under-engineered (looking at you, ZX80), or over-engineered with expensive dual port memory. It was just an elegant solution where good enough was actually good enough.