VintageVic

Experienced Member

Okay,

so I have a couple of MB 8128-15 (2kBx8) RAM chips and I can pull one more from donor 1541 pcb.

Question is, how to build 3kB memory expansion for the Vic?

Best approach I believe, is to use expansion slot pins to make connections. These I mean:

www.c64-wiki.com

www.c64-wiki.com

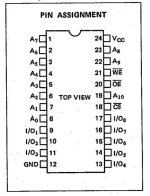

I've attached MB8128 pinout here. I suppose I will connect:

- A0 - A10 pins to the Address bus

- I/O 1 - I/O 8 to the data bus

- gnd and Vcc are obvious...

- pin 18CS to the expansion slot pin 14 (RAM1), pin 15 (for RAM2) and pin 16 (for RAM3)

but... what about pins 20 OutputEnable and 21 WriteEnable for each chip?

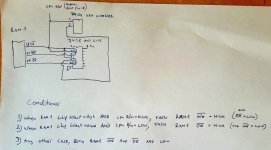

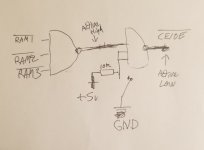

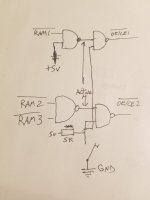

I guess I need one (or more) logic chip(s) that checks for instance if RAM1 CS is high then

it makes either WE or OE high on RAM1 depending on how CPU R/W is set (at expansion slot pin 18)?

I could probably figure this out on my own too... being first timer I'd be making things too complicated.

This must have already been figured out, so if you know, please share your knowledge here .

.

Also, I'd like to add on/off switch to run software that are made for unexpanded VIC. I guess simpliest

solution is to cut power for all chips at pin 24 for this purpose.

Notes:

I know I will be wasting the extra 1kb ram on each chip, since these are 2kb chips. It does not matter,

since I have these memory chips to use at my disposal.

I have already tried and succeeded to make 32kb ram expansion for blocks 1-5 using instructions

found online. I now want to learn how to add this 3kB extra.

so I have a couple of MB 8128-15 (2kBx8) RAM chips and I can pull one more from donor 1541 pcb.

Question is, how to build 3kB memory expansion for the Vic?

Best approach I believe, is to use expansion slot pins to make connections. These I mean:

Expansion port VIC20 - C64-Wiki

I've attached MB8128 pinout here. I suppose I will connect:

- A0 - A10 pins to the Address bus

- I/O 1 - I/O 8 to the data bus

- gnd and Vcc are obvious...

- pin 18CS to the expansion slot pin 14 (RAM1), pin 15 (for RAM2) and pin 16 (for RAM3)

but... what about pins 20 OutputEnable and 21 WriteEnable for each chip?

I guess I need one (or more) logic chip(s) that checks for instance if RAM1 CS is high then

it makes either WE or OE high on RAM1 depending on how CPU R/W is set (at expansion slot pin 18)?

I could probably figure this out on my own too... being first timer I'd be making things too complicated.

This must have already been figured out, so if you know, please share your knowledge here

Also, I'd like to add on/off switch to run software that are made for unexpanded VIC. I guess simpliest

solution is to cut power for all chips at pin 24 for this purpose.

Notes:

I know I will be wasting the extra 1kb ram on each chip, since these are 2kb chips. It does not matter,

since I have these memory chips to use at my disposal.

I have already tried and succeeded to make 32kb ram expansion for blocks 1-5 using instructions

found online. I now want to learn how to add this 3kB extra.