Dwight Elvey

Veteran Member

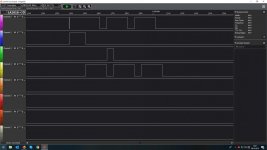

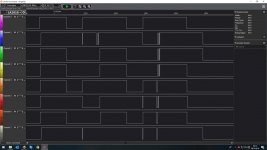

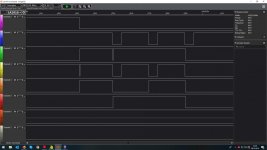

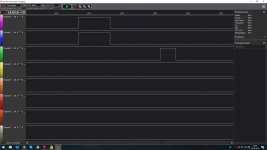

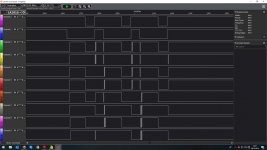

Sorry, i was on the false pin with psync. I have to say, i bought the logic analyzer before a few weeks and it´s the first time to work with it..I´ll now check again the databus. Psync goes from low to high and not from high to low. What do you think about that ?

View attachment 56504

So, C3 and the MSB and LSB are there. I think, there is something wrong in the 8t97 area ?!

THX

Jan

I think it was an error in the drawing. It is a PSYNC\ so falling signal is correct as you are seeing. I posted before you. Are you saying you see the correct C3 and address bits on the data lines? It is PSYNC positive on the mother board.It is inverted once to U13-8.

Dwight