Steve Toner

Experienced Member

I recently acquired a KDJ11-DB board which appears to be from 1991, based on the date codes on the chips. Put it together with an H9278-A backplane, MeanWell RD-85A power supply, a 3U rack mount case from Circuit Specialists and homebrew front & rear panel (or cab kit to use the DEC term) and here is the result:

This may offend the purists, but finding a proper DEC enclosure is a bit problematic...

The keyswitch controls boot select jumper W22 so that if jumpers W2, 3, 5, and 8 are installed, it will autoboot with the switch off and enter console mode with the switch on. The slot above the LEDs is for an SD card - I am planning to use Peter Schranz's RLV12 emulator to provide mass storage.

Here's a rear view:

If jumpers W2, 3, 5, and 8 are left unjumpered then the boot option switch can be used to select the desired boot option. I didn't do a fancy hex display for the status LEDs, but instead brought them (all seven of them!) out to individual LEDs. Baud rate for the two serial ports is selected by a rotary switch and the currently selected rate is displayed on an LED character display. These displays are entirely optional, and the rates corresponding to each switch value are printed on the board.

The LED displays don't photograph well, but they do look very nice in real life.

Interior layout:

The backplane is mounted using some scrap alumim(i)um leftover from other projects. The card guides are machined from acetal.

Detail view showing LTC module, front panel, and power connections to backplane:

The LTC is generated with an optoisolator, and the front panel signals are generated by a PIC16F1615 microcontroller. The raw LTC signal is fed into a Schmitt Trigger input on the microcontroller and regenerated before being sent to the bus. This may introduce some jitter into the signal (but coming from the power line, it's probably got plenty of jitter to begin with), but it allows the microcontroller to detect a loss of power by the absence of LTC edges and generate the aprropriate power-down sequence.

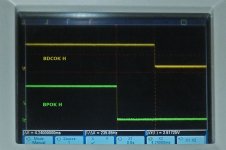

Power up sequence. Note the 72msec delay between BDCOK and BPOK:

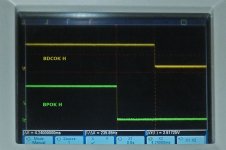

Power loss detection. BPOK is dropped approximately 50 msec after loss of BEVNT (LTC) signal:

and then BDCOK drops about 4 msec later:

The power supply is supposed to have enough reserve to allow the system to run for at least 3 msec after BPOK drops. With this configuration (just the CPU board installed), there is approximately 100 msec of reserve...

This may offend the purists, but finding a proper DEC enclosure is a bit problematic...

The keyswitch controls boot select jumper W22 so that if jumpers W2, 3, 5, and 8 are installed, it will autoboot with the switch off and enter console mode with the switch on. The slot above the LEDs is for an SD card - I am planning to use Peter Schranz's RLV12 emulator to provide mass storage.

Here's a rear view:

If jumpers W2, 3, 5, and 8 are left unjumpered then the boot option switch can be used to select the desired boot option. I didn't do a fancy hex display for the status LEDs, but instead brought them (all seven of them!) out to individual LEDs. Baud rate for the two serial ports is selected by a rotary switch and the currently selected rate is displayed on an LED character display. These displays are entirely optional, and the rates corresponding to each switch value are printed on the board.

The LED displays don't photograph well, but they do look very nice in real life.

Interior layout:

The backplane is mounted using some scrap alumim(i)um leftover from other projects. The card guides are machined from acetal.

Detail view showing LTC module, front panel, and power connections to backplane:

The LTC is generated with an optoisolator, and the front panel signals are generated by a PIC16F1615 microcontroller. The raw LTC signal is fed into a Schmitt Trigger input on the microcontroller and regenerated before being sent to the bus. This may introduce some jitter into the signal (but coming from the power line, it's probably got plenty of jitter to begin with), but it allows the microcontroller to detect a loss of power by the absence of LTC edges and generate the aprropriate power-down sequence.

Power up sequence. Note the 72msec delay between BDCOK and BPOK:

Power loss detection. BPOK is dropped approximately 50 msec after loss of BEVNT (LTC) signal:

and then BDCOK drops about 4 msec later:

The power supply is supposed to have enough reserve to allow the system to run for at least 3 msec after BPOK drops. With this configuration (just the CPU board installed), there is approximately 100 msec of reserve...