No, I understand that the chips are not controllers.

I read the datasheets for them. I understand that these chips do some kind of data-scrambling and channel-switching "magic" to turn the information in memory into something the CPU understands.

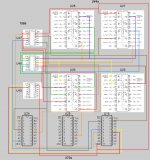

They don't "scramble" anything. The '244 is literally just a valve. (Or maybe "two valves" because it has a separate control "handle" for each 4 bits of the total 8 bits it handles.) The inputs, usually designated "1A(1-4)" and "2A(1-4)" on the datasheets, are controlled by the signals "1G" and "2G" respectively. If the "G" for those four bits is low the input state (high or low) is presented on "1Y(1-4)" or "2Y(1-4)" respectively; if "G" is high the outputs assume a "high impedance" state which essentially renders the device invisible. (Which means a downstream device either gets high or low from another device, a pull up/pull down resistor, or just floats.) When you see a '244 in a circuit the "G"s are often tied to ground, which means it's basically just acting like an "amplifier" for the input signal. If it *is* controlled it's usually because there's something else connected to the output side and the 244' is acting as part of a multiplexer.

(For instance, a pair of '244s could be used to do roughly the same job as a pair of 74LS157 Quad 2-input multiplexers, IE, either could be used to decide if the 8 bits to be asserted on "Bus Z" were sourced from "source X" or "source Y". The control circuitry would just be slightly different.)

A '373 does the same thing (IE, it can act as a "valve" because it has an output enable signal to tri-state the output, although in its case it applies to all 8 outputs simultaneously, not two groups of four) except it can also "latch" what's coming out the other side. IE, if output enable is "low" then what comes out on the "O" outputs matches the "D" inputs in real time if latch is "high", but if latch goes "low" the value on D0-7 is latched into into registers "Q0-7", and that value is what comes out on "O0-7" for as long as latch is held low, regardless of what happens to "D0-7". Again, nothing gets "scrambled"

I'm just contemplating if tying the A16 and A17 data lines into a free spot in the logic circuitry will make it work, like changing how a floppy drive interprets grounded setting pins. (This is tentative, though. I know it might not be as simple as that.) The other data lines seem to be added already.

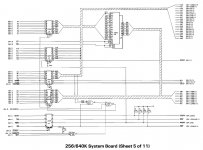

No. A16 and A17 are not "data lines", they're address lines, and they're no doubt already "connected to the logic circuitry" that's used to select which set of RAS/CAS lines are active because decoding A16 and A17 is how you tell which page of 64k you're on. (IE, like this: 64K takes 16 bits to represent; IE, if the smallest chips the Sanyo supports are 64K we can completely ignore A0-15. That leaves A16-A19. That's 4 bits, which allows 16 possibilities, which means a total of 16 possible pages of 64k to think about. When you only have 4 banks and they all have 64k then this is what your decoding needs to care about to decode your RAM, which should reside in the bottom 256k of the possible 1024k of address space:

A19 - Has to be a zero

A18 - Has to be a zero

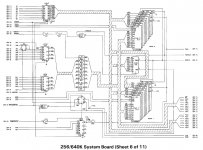

(This is what U48 does on the 256k 5150 board does. If A19 and or A18 are not a zero then the '138s that decide what bank is selected don't do anything.)

A17 and A16: Again referencing the 5150 schematics, these are decoded by U47 and U65. These are set up to act as 1-in-4 decoders (see how half the outputs are "wasted"; looking at the IBM schematics it looks like IBM used them instead of '139s because they're relying on the multi-conditional output enable gates to add additional conditions beyond the address to gate the assertion of these signals) and which set of CAS/RAS signals is active, IE, which bank is enabled, is *directly based* on the state of A17 and A16. There's nothing more to do with them.

To make your Sanyo access 256k in a bank you actually need to disconnect A16 and A17 directly from the CAS/RAS decoders (assuming that's how they're actually wired, that's why I said you need to figure out if there's a PROM, additional decoding, or *what* there) and instead generate a truth table something like this:

(x = "don't care".)

Code:

A19 A18 A17 A16 : Desired state

0 0 x x : Enable RAS/CAS for bank 1 (256k, starting address 00000h)

0 1 x x : Enable RAS/CAS for bank 2 (256k, starting address 40000h)

1 0 0 0 : Enable RAS/CAS for bank 3 (64k, starting address 80000h)

1 0 0 1 : Enable RAS/CAS for bank 4 (64k, starting address 90000h)

All other states : Nothing enabled.

Note also that the first layer of decoding, U48 on the 5150, which is "active low" when *any* of the banks should be active, was also used as a control signal for several items, including a bidirectional '245 buffer in front of the RAM data lines, so whatever you do on the Sanyo to fix the RAS/CAS decoding also still needs to produce that total "memory is active, period" signal. So, again, it's A18 and A19 that you need to start decoding in more detail to get more than 256k, and that is where it matters critically how the Sanyo is doing it *now*.