daver2

10k Member

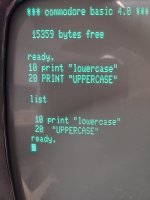

Look on the schematics for the /CAS0 and /CAS1 signals. /CAS0 drives the lower bank of RAM (odd-numbered UA devices) whilst /CAS1 drives the upper bank of RAM (even-numbered UA devices).

It may not be the RAM itself of course - the data bus buffers are notorious for failing, as are the address multiplexers. I have also seen the refresh counters fail - this causes some 'interesting' faults!

Dave

It may not be the RAM itself of course - the data bus buffers are notorious for failing, as are the address multiplexers. I have also seen the refresh counters fail - this causes some 'interesting' faults!

Dave