Eudimorphodon

Veteran Member

I'm still sort of a newb at this whole "programmable logic" thing, so I have this strong feeling I'm probably missing a really obvious and cool way to accomplish a thing. So here's a question for the wizards: what's the best strategy for implementing non-power-of-2 clock dividers in a GAL?

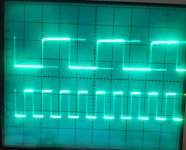

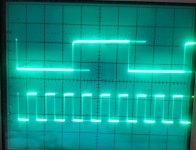

A project that I'm slowly plugging away on, at least in the back of my head, is an idea for a kind of "retro-recreation" of a TRS-80 Model III computer, and for it it'd be nice if I could derive 4mhz and 2mhz clocks from a master 12mhz pixel clock in the video section. Banging on it for a while this is the best divide-by-three equation I could come up with:

It takes four output registers to implement; two for a 2-bit counter, one for a reset-on-2, and one to stretch the reset another half input cycle to make it a 50% duty cycle. (If I would be happy with a 33/66 duty cycle then I could get rid of COUT and use A directly.)

Is there a better way to do this, or is this good enough for government work?

A project that I'm slowly plugging away on, at least in the back of my head, is an idea for a kind of "retro-recreation" of a TRS-80 Model III computer, and for it it'd be nice if I could derive 4mhz and 2mhz clocks from a master 12mhz pixel clock in the video section. Banging on it for a while this is the best divide-by-three equation I could come up with:

Code:

GAL16V8 ; Divide by three test

DIVTHREE ;

Clock CL NC NC NC NC NC NC NC GND

/OE A COUT NC NC NC NC Q1 Q0 VCC

Q0.R = /A * /Q0

Q1.R = /A * /Q1 * Q0

+ /A * Q1 * /Q0

A = /Q0 * Q1

COUT = A

+ /Q0 * /Q1 * CL

DESCRIPTION

this is a divide-by-three circuit, 50% duty cycle

registered outputs are signed with the postfix .R

Q0 and Q1 are a two bit counter.

A goes high when Qx=2, causing counter reset to 0 on next clock, skipping Qx=3

COUT is high when A is high (Qx = 2) + 1/2 of (Qx=0)It takes four output registers to implement; two for a 2-bit counter, one for a reset-on-2, and one to stretch the reset another half input cycle to make it a 50% duty cycle. (If I would be happy with a 33/66 duty cycle then I could get rid of COUT and use A directly.)

Is there a better way to do this, or is this good enough for government work?