Koolstar42

Experienced Member

Hi all

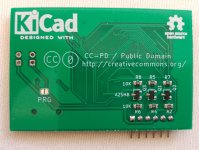

I recently finished my latest project, which is a i8080 CP/M computer, emulated in an ATMega88 on a circuit board the size of about half a credit card.

This originally is the brainchild of Takashi Toyoshima, but fixed and drastically improved upon. It now has 128kByte of banked memory, accepts SC and HC SD cards, has RTS handshaking and is multiboot.

In essence it runs CP/M 2.2 and CP/M 3.1 at an apparent clock of 2.5-3.5 MHz. It uses a micro SD card with up to 254 8Mbyte disk 'Volumes', which can be mounted on each of the 3 system drives A:-C:

When a volume is prepared with a working system track it will be bootable.

Initially only volume 2 and 3 are mad bootable. Volume 2 with CP/M 2.2 and Volume 3 with CP/M 3.1.

When a certain volume is booted, the following 2 are mounted on B: and C:, but this can be changed with a supplied MOUNT tool.

Volumes can be formatted, and made bootable with a PUTSYS tool.

Volumes 10-12 contain a collection of programs like dbaseii, wordstar, asssemblers, interpreters and compilers etc as well as the infocom games and ADV.

Volumes 20-57 contain the complete CPM/UG and SIGM libraries, both archived and extracted. The rest of the volumes is currently unused.

The system has only one serial interface to the outside world. It is fixed at 38400 baud with RTS handshake. It is plug-compatible with FTDI interface boards but accepts both 3.3 and 5v adapters. The board is powered with 5v (primarily by the interface) and the i/o is protected with level shifters. Average power consumption is about 10 mA

And now the best part, This system can be built for less than 10 dollars (used to be 5, but times change...) I am aware that not everybody is comfortable soldering SMD parts, therefore I may be willing to build one for you. However I only have a limited amount of parts available. And shipping is a pita nowadays.

And of course all the associated files, Kicad, gerbers, source files disk images etc are available if you want to do it yourself.

Rienk

I recently finished my latest project, which is a i8080 CP/M computer, emulated in an ATMega88 on a circuit board the size of about half a credit card.

This originally is the brainchild of Takashi Toyoshima, but fixed and drastically improved upon. It now has 128kByte of banked memory, accepts SC and HC SD cards, has RTS handshaking and is multiboot.

In essence it runs CP/M 2.2 and CP/M 3.1 at an apparent clock of 2.5-3.5 MHz. It uses a micro SD card with up to 254 8Mbyte disk 'Volumes', which can be mounted on each of the 3 system drives A:-C:

When a volume is prepared with a working system track it will be bootable.

Initially only volume 2 and 3 are mad bootable. Volume 2 with CP/M 2.2 and Volume 3 with CP/M 3.1.

When a certain volume is booted, the following 2 are mounted on B: and C:, but this can be changed with a supplied MOUNT tool.

Volumes can be formatted, and made bootable with a PUTSYS tool.

Volumes 10-12 contain a collection of programs like dbaseii, wordstar, asssemblers, interpreters and compilers etc as well as the infocom games and ADV.

Volumes 20-57 contain the complete CPM/UG and SIGM libraries, both archived and extracted. The rest of the volumes is currently unused.

The system has only one serial interface to the outside world. It is fixed at 38400 baud with RTS handshake. It is plug-compatible with FTDI interface boards but accepts both 3.3 and 5v adapters. The board is powered with 5v (primarily by the interface) and the i/o is protected with level shifters. Average power consumption is about 10 mA

And now the best part, This system can be built for less than 10 dollars (used to be 5, but times change...) I am aware that not everybody is comfortable soldering SMD parts, therefore I may be willing to build one for you. However I only have a limited amount of parts available. And shipping is a pita nowadays.

And of course all the associated files, Kicad, gerbers, source files disk images etc are available if you want to do it yourself.

Rienk