Hi D.B. ... how can I contact you offline?And vcc is not an on/off power switch. depending on the IC interesting things can occur even with it disconnected...

Upcoming Events:

- VCF South West - June 14 - 16, Davidson-Gundy Alumni Center at University of Texas at Dallas

- VCF West - Aug 2 - 3, Computer History Museum, Mountain View, CA

- VCF Midwest - Sept 7 - 8 2024, Schaumburg, IL

- VCF SoCal - Mid February 2025, Location TBD, Southern CA

- VCF East - April 2025, Infoage Museum, Wall NJ

-

Please review our updated Terms and Rules here

- Forums

- Companies

- IBM Computers, PCs, Clones and Descendants

- PCs and Clones (XT and early AT class machines)

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Switching between two 8088 CPUs

- Thread starter n0p

- Start date

GloriousCow

Experienced Member

- Joined

- Oct 28, 2022

- Messages

- 65

Hi D.B. ... how can I contact you offline?

Er, why would you need to?

Ruud

Veteran Member

Private mail, click on the avatar - new direct message, should do.Hi D.B. ... how can I contact you offline?

daver2

10k Member

They can't. They are still under moderation - so can't initiate DMs.

They can respond to them...

Dave

They can respond to them...

Dave

1ST1

Veteran Member

Hugo Holden

Veteran Member

There is a possible way I think that could work , it would have to be tried. I have never tried this myself with a CPU, but I have with some logic chips, but it would be something I would try before making a more complex system to switch in more than one CPU.

It definitely won't work doing by de-powering one CPU, because what happens is when a pin is pulled high on the non powered CPU from the powered one, current is sourced by the input protect diodes into the non powered chip die. Actually similar things happen in that if you switch off the CPU's support chips, then their inputs draw current from the CPU or other chips driving them, because often the internal resistance of the power supply system can be fairly low when de-powered, not so much if open circuited though.

(Coincidentally, I just had a really interesting issue with an mcu, that draws a significant glitch of current when its support chips are de-powered when the unit powered down. In this condition the MCU itself is powered by a backup battery, but the glitch was pulling the supply pin low enough to corrupt the RAM in the mcu because of the higher internal resistance of the battery supply)

Also, everyone is familiar with the story of the cmos chip that still works, even though you forgot to connect its power pin to V+, because it becomes powered by one of the other inputs which is high via the substrate diode/s, so if all pins go low, the chip stops.

In any case, what you could try:

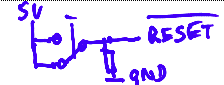

With the two CPU's wired in parallel, you open circuit the earth pin/s of the CPU that you don't want (and also any other pin from the CPU package that are connected directly to ground, connect all these together to the switch).

The idea is that you create a situation where the remaining connected (deactivated CPU) pins cannot sink any significant current to ground. You can use a switch or a transistor acting as a switch, then the CPU's GND pin/s pull up to +5V with the switch open. This de-powered chip could attempt to be powered by pins pulled high by devices they are connected to, but they will not draw any significant current because the input pin is a diode drop below the +5V supply. Meaning they would have to go over 5V to get any current into the chip's pin.

But, in this condition, can any pin on the deactivated CPU sink any current from the other working CPU pins ?

There could be a current pathway from one pin, to another pin in the package, but given that the CPU that is off is un-powered and has no solid ground connection, it is likely to be only a very weak interaction and not affect any of the lines on the active CPU. The input substrate diodes would conduct with the input pin pulled low, so that would create a weak pullup effect (most likely), if it was too high, then a switch could be made to open circuit both the ground and power pins of the deactivated CPU. That would be an interesting experiment.

As mentioned, this is a possible way that could work, it would need to be found by experiment and looking with the scope if there were any significant effects at all from the deactivated CPU affecting the active one. And if it did work, you would still need a reset for the selected active one.

It definitely won't work doing by de-powering one CPU, because what happens is when a pin is pulled high on the non powered CPU from the powered one, current is sourced by the input protect diodes into the non powered chip die. Actually similar things happen in that if you switch off the CPU's support chips, then their inputs draw current from the CPU or other chips driving them, because often the internal resistance of the power supply system can be fairly low when de-powered, not so much if open circuited though.

(Coincidentally, I just had a really interesting issue with an mcu, that draws a significant glitch of current when its support chips are de-powered when the unit powered down. In this condition the MCU itself is powered by a backup battery, but the glitch was pulling the supply pin low enough to corrupt the RAM in the mcu because of the higher internal resistance of the battery supply)

Also, everyone is familiar with the story of the cmos chip that still works, even though you forgot to connect its power pin to V+, because it becomes powered by one of the other inputs which is high via the substrate diode/s, so if all pins go low, the chip stops.

In any case, what you could try:

With the two CPU's wired in parallel, you open circuit the earth pin/s of the CPU that you don't want (and also any other pin from the CPU package that are connected directly to ground, connect all these together to the switch).

The idea is that you create a situation where the remaining connected (deactivated CPU) pins cannot sink any significant current to ground. You can use a switch or a transistor acting as a switch, then the CPU's GND pin/s pull up to +5V with the switch open. This de-powered chip could attempt to be powered by pins pulled high by devices they are connected to, but they will not draw any significant current because the input pin is a diode drop below the +5V supply. Meaning they would have to go over 5V to get any current into the chip's pin.

But, in this condition, can any pin on the deactivated CPU sink any current from the other working CPU pins ?

There could be a current pathway from one pin, to another pin in the package, but given that the CPU that is off is un-powered and has no solid ground connection, it is likely to be only a very weak interaction and not affect any of the lines on the active CPU. The input substrate diodes would conduct with the input pin pulled low, so that would create a weak pullup effect (most likely), if it was too high, then a switch could be made to open circuit both the ground and power pins of the deactivated CPU. That would be an interesting experiment.

As mentioned, this is a possible way that could work, it would need to be found by experiment and looking with the scope if there were any significant effects at all from the deactivated CPU affecting the active one. And if it did work, you would still need a reset for the selected active one.

Last edited:

jplr

Experienced Member

@Hugo Holden,

I am a noob in electronics and you are a giant, here is my question:

The output Pin of CMOS CPU is not really symmetric, Vdd is connected to a P-MOS and Gnd to a N-MOS transistor. Is this the reason why removing Vdd would have different effects than removing Gnd?

What about leakage currents that happen in underpowered MOS transistors?

I am a noob in electronics and you are a giant, here is my question:

The output Pin of CMOS CPU is not really symmetric, Vdd is connected to a P-MOS and Gnd to a N-MOS transistor. Is this the reason why removing Vdd would have different effects than removing Gnd?

What about leakage currents that happen in underpowered MOS transistors?

jplr

Experienced Member

Another question, you said "It definitely won't work doing by de-powering one CPU, because what happens is when a pin is pulled high on the non powered CPU from the powered one, current is sourced by the input protect diodes into the non powered chip die. "

Won't the same phenomenon happen when the Gnd connection is switched off?

Won't the same phenomenon happen when the Gnd connection is switched off?

cjs

Experienced Member

That absolutely will not work. A couple of other folks have already described the problem with it:Let's say i want to connect two 8088 CPU to the board, NEC V20 and cycle-exact 8088-clone.

All lines, except 5V Vcc, are connected to both.

Will supplying Vcc to only one work? I mean won't second CPU internals mess with it?

And vcc is not an on/off power switch. depending on the IC interesting things can occur even with it disconnected...

This is not limited to CMOS; I once spent about ten minutes debugging a 74LS86 XOR gate that was mostly, but not entirely, doing its job correctly. I finally realised what was wrong when I noticed that the Vcc pin wasn't connected. It was powered pretty near darn fine just from the input pins.It definitely won't work doing by de-powering one CPU, because what happens is when a pin is pulled high on the non powered CPU from the powered one, current is sourced by the input protect diodes into the non powered chip die....

Also, everyone is familiar with the story of the cmos chip that still works, even though you forgot to connect its power pin to V+, because it becomes powered by one of the other inputs which is high via the substrate diode/s, so if all pins go low, the chip stops.

An IC is not a set of discrete pins that do only what the documentation says; it's a circuit that has all pins eventually connected to each other through various transistors and whatnot. The only ways to make sure it's properly "disconnected" are to completely disconnect all the signal pins from the rest of the system or to use whatever methods the IC provides for disconnecting itself, such as asserting signals to tri-state buses.

This would be an interesting experiment to perform if you're into that kind of experimentation, but as a way of achieving the aim of the OP it's unlikely to work. The ground and power pins are simply not the sole sources of ground and power for an IC; depending on the design it can sink current from potentially any pin that's at a level sort-of-towards Vcc and source current to potentially any pin that's at a level sort-of-towards ground.In any case, what you could try:

With the two CPU's wired in parallel, you open circuit the earth pin/s of the CPU that you don't want (and also any other pin from the CPU package that are connected directly to ground, connect all these together to the switch).

The idea is that you create a situation where the remaining connected (deactivated CPU) pins cannot sink any significant current to ground.

I think this should actually work. You could also consider the SN74CBT16233 multiplexer which is very similar to the SN74CBT16390 except for the control signals. You could use a simple DPDT toggle switch to control the input of the analog multiplexer and possibly the supply of the 8088 / V20 sockets. Then you leave all ground pins connected, and connect all other signals through the analog multiplexers.Did some dig on multiplexers.

Will 3x SN74CBT16390 do?

Datasheet https://www.ti.com/lit/ds/symlink/sn74cbt16390.pdf

For me it looks like exact tool for that.

Though the idea is straightforward, it still means designing a PCB with at least 3 56-pin SMD devices and 3 40-pin sockets/headers.

GloriousCow

Experienced Member

- Joined

- Oct 28, 2022

- Messages

- 65

I just did a test with a Harris 80c88. It will happily run with VCC pin completely disconnected

Eudimorphodon

Veteran Member

It remains that the “right” way to do this would be via the request/grant mechanism. Using that would eliminate any need for a pile of multiplexers or electrically sketchy power switching monkeyshines.

This mechanism is already used in any XT that has a math coprocessor; the pinout of the 8087 socket in your standard XT is very nearly identical to the main CPU and most of the pins are connected in parallel, and the 8087 works by lurking in the background listening to the data and CPU status pins. When it sees an 8087 instruction on the bus during an instruction fetch cycle it grabs it, and if the instruction requires pulling in additional bytes or writing stuff back to memory it takes control by pulling the RQ line telling the main CPU to release control.

The 8087 cheats a little bit on support circuitry, obviously, by having the state machine that determines when it’s the proper time to snooze the main CPU integrated internally, but since the goal here isn’t to dynamically switch between the CPUs it might be as simple as just using a multiplexer to hold the RQ lines of the CPU you don’t want active on power-up? I’d have to dig into the fat manual to try to make a fully educated guess.

This mechanism is already used in any XT that has a math coprocessor; the pinout of the 8087 socket in your standard XT is very nearly identical to the main CPU and most of the pins are connected in parallel, and the 8087 works by lurking in the background listening to the data and CPU status pins. When it sees an 8087 instruction on the bus during an instruction fetch cycle it grabs it, and if the instruction requires pulling in additional bytes or writing stuff back to memory it takes control by pulling the RQ line telling the main CPU to release control.

The 8087 cheats a little bit on support circuitry, obviously, by having the state machine that determines when it’s the proper time to snooze the main CPU integrated internally, but since the goal here isn’t to dynamically switch between the CPUs it might be as simple as just using a multiplexer to hold the RQ lines of the CPU you don’t want active on power-up? I’d have to dig into the fat manual to try to make a fully educated guess.

daver2

10k Member

>>> I just did a test with a Harris 80c88. It will happily run with VCC pin completely disconnected

I don't really think you meant that (did you)?

Did you mean with two 80c88 chips in parallel and ONE with the VCC disconnected?

Dave

I don't really think you meant that (did you)?

Did you mean with two 80c88 chips in parallel and ONE with the VCC disconnected?

Dave

GloriousCow

Experienced Member

- Joined

- Oct 28, 2022

- Messages

- 65

>>> I just did a test with a Harris 80c88. It will happily run with VCC pin completely disconnected

I don't really think you meant that (did you)?

Did you mean with two 80c88 chips in parallel and ONE with the VCC disconnected?

Dave

I'm not attempting to run two 80c88's in parallel. We were just discussing whether VCC was enough to 'disable' one of the CPUs, and it least for the CMOS version it is not.

GloriousCow

Experienced Member

- Joined

- Oct 28, 2022

- Messages

- 65

It remains that the “right” way to do this would be via the request/grant mechanism. Using that would eliminate any need for a pile of multiplexers or electrically sketchy power switching monkeyshines.

This mechanism is already used in any XT that has a math coprocessor; the pinout of the 8087 socket in your standard XT is very nearly identical to the main CPU and most of the pins are connected in parallel, and the 8087 works by lurking in the background listening to the data and CPU status pins. When it sees an 8087 instruction on the bus during an instruction fetch cycle it grabs it, and if the instruction requires pulling in additional bytes or writing stuff back to memory it takes control by pulling the RQ line telling the main CPU to release control.

The 8087 cheats a little bit on support circuitry, obviously, by having the state machine that determines when it’s the proper time to snooze the main CPU integrated internally, but since the goal here isn’t to dynamically switch between the CPUs it might be as simple as just using a multiplexer to hold the RQ lines of the CPU you don’t want active on power-up? I’d have to dig into the fat manual to try to make a fully educated guess.

I think this is the right track. The request/grant mechanism follows roughly the same rules as prefetch aborts:

For a request to be honored, all of these conditions must be true:

- Request occurs on or before T2.

- Current cycle is not the low bit of a word.

- Current cycle is not the first acknowledge of an interrupt acknowledge sequence.

- A locked instruction is not currently executing.

Another potential wrinkle is the 8288. It was not designed to serve two CPU's. It's not enough to just release the bus, we have to either shunt the S0-S2 lines from cpu to cpu, or ... perhaps have two 8288's as well...

daver2

10k Member

I'm not attempting to run two 80c88's in parallel. We were just discussing whether VCC was enough to 'disable' one of the CPUs, and it least for the CMOS version it is not.

Got you. So you disconnected the VCC pin on the 80c88 and it was quite happy to run with the residual voltage from a logic HIGH on another pin powering it.

Dave

GloriousCow

Experienced Member

- Joined

- Oct 28, 2022

- Messages

- 65

Got you. So you disconnected the VCC pin on the 80c88 and it was quite happy to run with the residual voltage from a logic HIGH on another pin powering it.

Dave

I don't know how happy it was, but it ran. This was at very low frequency. I can attempt with an AMD D8088 and see if it behaves the same.

I just happened to be well-equipped to perform this test as I have an 8088 Arduino MEGA hat which I had modified for an Arduino GIGA by snipping off the 5v pin. I normally bridge the 3v and 5v lines so that the chip gets 3v, which it tolerates.

I just pulled the jumper out.

cjs

Experienced Member

Well, it's current that powers the chip, not voltage. And current that the chip sinks from all source is always what's powering it; when the chip sinks a certain amount of current from the data bus lines as it reads the data bus, that current contributes to powering the chip and slightly less will be drawn from the Vcc pin than if it were writing the data bus.Got you. So you disconnected the VCC pin on the 80c88 and it was quite happy to run with the residual voltage from a logic HIGH on another pin powering it.

The degree to which any particular pin is able to provide power to a chip varies with the chip design, of course. But as someone mentioned earlier, CMOS chips generally have protection diodes on most pins that connect directly to the Vcc; if you supply a higher voltage than Vcc on one of those pins current will flow from that pin to the Vcc pin. Supplying such a higher voltage (with current limiting via a series resistor) can be part of the design of a system that's, e.g., using a 3.3 V part in an otherwise 5 V system. In such a case you can actually have a chip's Vcc pin sourcing power, i.e., acting as a power supply for other devices in the system. (And if you're using a linear regulator, you'd better hope the other devices draw that current, or you'll find yourself sourcing current into the output of the regulator, which will tend to make it rather unhappy.)

daver2

10k Member

Well, you will only get a current flow if there is a potential difference and something capable of conducting electrons (or holes) between the potential difference...

Dave

Dave

cjs

Experienced Member

Not just a potential difference, but also a source that can maintain that potential difference.Well, you will only get a current flow if there is a potential difference....

In other words, a current source.

(You can think of a current source as something that maintains a voltage difference, but I don't really like to do that because no real current source can always maintain a voltage difference; there's always a limit on the current it can supply.)