daver2

10k Member

In cases like this, it is back to the NOP generator to work out if there is anything wrong with the address bus or address decoding...

Dave

Dave

| VCF West | Aug 01 - 02 2025, | CHM, Mountain View, CA |

| VCF Midwest | Sep 13 - 14 2025, | Schaumburg, IL |

| VCF Montreal | Jan 24 - 25, 2026, | RMC Saint Jean, Montreal, Canada |

| VCF SoCal | Feb 14 - 15, 2026, | Hotel Fera, Orange CA |

| VCF Southwest | May 29 - 31, 2026, | Westin Dallas Fort Worth Airport |

| VCF Southeast | June, 2026 | Atlanta, GA |

OK. Will do but will be tomorrow night for me now.back to the NOP generator

This is the 8032090Can you remind me what the part number of the PCB again is please

Point taken, although having just checked the same with my scope, I'm still seeing nothing at all.In other words it is possible that what you are seeing on the logic analyzer is lying to you

Towards 1 secondUsually this is about half a second or more

Nothing - this all started when 'something' went wrong and i lost the screen. VDRIVE and HDRIVE have nothing and CRTC never enables.what are you observing on the screen

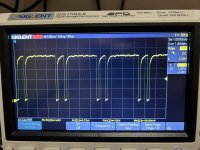

you should observe some form of /CS signal on the CRTC (pin 25) when you reset the PET (or power it up).

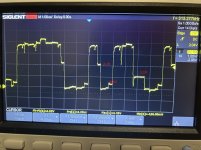

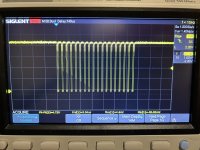

1 mHz good (999.825)check for a 1 MHz clock on pin 21 of the CRTC

22: 170 kHzactivity on pins 22, 23 and 24

CRTC not in socket.Is the CRTC in a socket?

1: 0.0319VCan you also check the power pins on the CRTC (pin 1 = 0V and pin 20 = +5V). Check both pins.

34: lowPins 34 to 40

All lowPins 4 to 13.

All lowPins 16-18.