Port89

Experienced Member

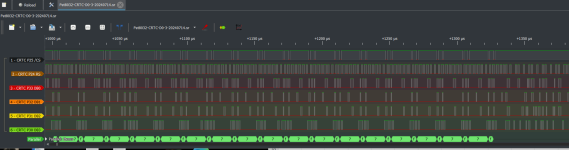

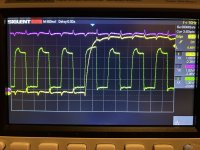

If so, I'm not keen to butcher my other PET at this point - is Hitachi 6845 an OK replacement (I see that discussed in other threads where the original MC doesn't suit) or do I specifically need to source the MOS one?I am going to call the CRTC dead...