Eudimorphodon

Veteran Member

If I understand correctly, the point is to avoid the infamous "TRS-80 snow", and also to avoid slowing down the CPU during accesses because cycle counting is a thing, etc. But if you put a super-fast Z80 in there, does cycle timing even matter anymore? At that point you might as well just put in wait states.

Well, it's a little more than snow avoidance; imagine if you had a TRS-80 Model 1 and were trying to run *code* from video memory; you'd probably end up with a mostly black screen. That's kind of what I'm trying to do here, make *all* the RAM in the system (potential) VRAM...

My first computer (kit computer) had what you call "unified" memory. The video circuit would ask the Z80 to give up the bus (by using BUSREQ), read the current video page and display it. At the end it would hand control back. So the CPU ran at half speed, but there was no snow.

The great thing with this system is that by using a certain OUT command, you could choose any part of memory to be the video page.

Yeah, and honestly if I wasn't trying to be (partially) TRS-80 compatible I think the "cost" of doing that on a completely novel architecture would probably be mostly fine; if the CPU were running at 10+mhz only half the time it'd feel mostly fast enough. The main drawback would be you'd probably need to blank the screen whenever you did high-speed I/O.

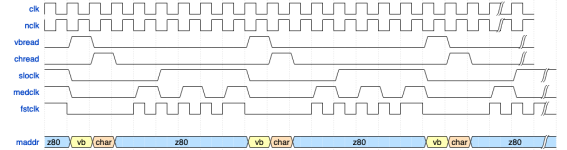

Poking around I stumbled across this javascript toy that lets you describe digital timing diagrams in the form of JSON files, and I used it to draw out roughly what I think I'm going to try programming into the GALs for the first attempt.

"vbread" and "chread" are the two cycles that per character that the video hardware needs access to memory; "vbread" is reading and latching the framebuffer for a pixel pattern or character value, and during "chread" that latched value is added to an address offset to get the actual pixels to latch into the output shift register. The "maddr" line represents what owns the address bus (and, effectively, data bus and memory control signals) for each clock period; the remaining 75% of the time the CPU gets control. This diagram shows three possible clocks for the CPU; "sloclk" is the pixel clock /8 and has a "normal" 50/50 duty cycle, "medclock" is effectively pixel clock divided by 3/8th by running the CPU running at pixel clock/2 half the time with every-third low duty cycle being 3x normal length, and "fstclock" gives you 5/8th full speed twith a kind of weird duty cycle bracketing the video reads.

(That last one is super aggressive and is too fast for the rated speed of the Z80s I have on hand so maybe I'll skip that one. It *feels* like it might be just possible to do 6/8th speed by fussing with the clock phases but it's pretty unnecessary; 5/8ths speed for the pixel clock I'm planning to use is going to be like 9mhz, which is a stupid fast TRS-80. The 3/8th speed is over 5mhz, which is about as fast as a Model I could ever go with a lot of hacking. )

I know from earlier testing that doing vbread and chread in single ticks seems to work fine, so... cautiously optimistic this might work? Nothing ventured nothing gained, I guess.