g4ugm

Veteran Member

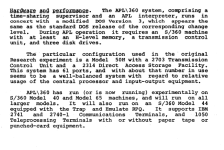

Most S/360 code runs on a S/370. Most S/370 code runs on any S/370. The whole point of S/360 was that any code could be ported to a bigger machine without change. The exception was the 360/20 but most folks don't consider that a S/360. Even if you had floating point code on a machine without floating point hardware there were simulators you could load to allow it to run, so its pretty pointless trying to decide which model an arbitrary piece of code came from.Yep, I hadn’t seen an S3 analysis yet, so I was gearing up with practice on what we knew so far on the S370 side. Actually I wasn’t certain on S360 vs S370 content - and was wondering if we could narrow it down to a more specific model ( and maybe find the original source that it came from ).

So if it’s S370 based then it’s some model 150 series? Also weird to think of a “weaker system” emulating a more powerful system ( ie 16bit PALM emulating 32bit mainframe ), but maybe that just shows how arbitrary categorizing the “bit-ness” of a system is. ( I think we talked before how the 1-bit Datapoint could still do a good amount of general purpose stuff )

The ability to emulate another system is a fundamental of property of any Turing Complete computer. So if a computer is Turing Complete and basically when we use the word computer in the modern sense its really shorthand for "Turing Complete Computer" it can emulate any other Turing Complete computer. Of course this assumes sufficient store is available and the result might be slow but it will eventually work