voidstar78

Veteran Member

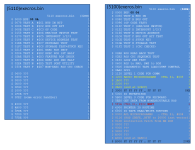

From the disassembled 5100 Executive ROS, here are all the devices it refers to via CTRL $1 (command to access the ROS addresses):

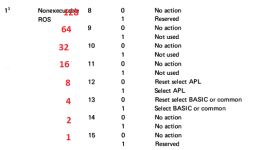

There is mostly #$08 and #$04 as expected, but what are #$02, #$88, #$84, #$82, #$00 ?

Line 542: 03D0 1108 CTRL $1, #$08 (BASIC)

Line 548: 03DA 1104 CTRL $1, #$04 (APL)

Line 2607: 1200 1108 CTRL $1, #$08

Line 4031: 1B6A 1108 CTRL $1, #$08

Line 11066: 502E 1108 CTRL $1, #$08

Line 11999: 55D6 1104 CTRL $1, #$04

Line 12114: 5698 1108 CTRL $1, #$08

Line 12918: 5BEE 1108 CTRL $1, #$08

Line 13361: 5F0A 1108 CTRL $1, #$08

Line 13366: 5F12 1104 CTRL $1, #$04

Line 13371: 5F1A 1102 CTRL $1, #$02 what

Line 13427: 5F76 1188 CTRL $1, #$88 ROS

Line 13432: 5F7E 1184 CTRL $1, #$84 are

Line 13437: 5F86 1182 CTRL $1, #$82 these

Line 13443: 5F90 1100 CTRL $1, #$00 ????

Line 18444: 8000 1104 CTRL $1, #$04

Line 19123: 84D4 1104 CTRL $1, #$04

(recall that whole section around $5FXX is IO Supervisor related stuff; and also only the "CTRL $1,#$02" might be valid, the rest could be bogus/misleading {perhaps actually data instead} -- but doesn't hurt to try 'em all :D )

I think if you plug some of those into the sample machine code for extracting ROS, we'll get some different responses.

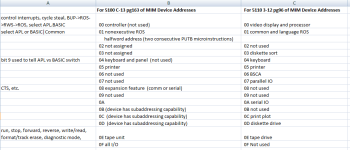

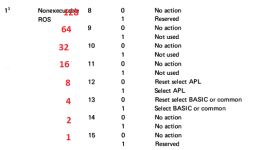

And yes, use of those values contradicts the 5100 MIM manual: (where only #$04 and #$08 should be defined)

I can't find a similar chart for the 5110's use of the CTRL opcode, but in Christian's notes:

"To extract another ROS alter the CTRL instruction at location 0B00, use #$08 for the BASIC ROS and #$02 for the Common ROS." (which is confusing/misleading since elsewhere in the manual, it does say BASIC and Common share the same address space).

Anyhow, that's the request: using Christian's sample to access ROS's, can anyone with a 5100 try plugging in #$02 (i.e. values besides #$04 and #$08) and see if a difference sequence of binary is copied to RWS? If so, that should be the missing ROS. I'm not sure it'll have 6K segments also, but it should be a total of about 18K.

There is mostly #$08 and #$04 as expected, but what are #$02, #$88, #$84, #$82, #$00 ?

Line 542: 03D0 1108 CTRL $1, #$08 (BASIC)

Line 548: 03DA 1104 CTRL $1, #$04 (APL)

Line 2607: 1200 1108 CTRL $1, #$08

Line 4031: 1B6A 1108 CTRL $1, #$08

Line 11066: 502E 1108 CTRL $1, #$08

Line 11999: 55D6 1104 CTRL $1, #$04

Line 12114: 5698 1108 CTRL $1, #$08

Line 12918: 5BEE 1108 CTRL $1, #$08

Line 13361: 5F0A 1108 CTRL $1, #$08

Line 13366: 5F12 1104 CTRL $1, #$04

Line 13371: 5F1A 1102 CTRL $1, #$02 what

Line 13427: 5F76 1188 CTRL $1, #$88 ROS

Line 13432: 5F7E 1184 CTRL $1, #$84 are

Line 13437: 5F86 1182 CTRL $1, #$82 these

Line 13443: 5F90 1100 CTRL $1, #$00 ????

Line 18444: 8000 1104 CTRL $1, #$04

Line 19123: 84D4 1104 CTRL $1, #$04

(recall that whole section around $5FXX is IO Supervisor related stuff; and also only the "CTRL $1,#$02" might be valid, the rest could be bogus/misleading {perhaps actually data instead} -- but doesn't hurt to try 'em all :D )

I think if you plug some of those into the sample machine code for extracting ROS, we'll get some different responses.

And yes, use of those values contradicts the 5100 MIM manual: (where only #$04 and #$08 should be defined)

I can't find a similar chart for the 5110's use of the CTRL opcode, but in Christian's notes:

"To extract another ROS alter the CTRL instruction at location 0B00, use #$08 for the BASIC ROS and #$02 for the Common ROS." (which is confusing/misleading since elsewhere in the manual, it does say BASIC and Common share the same address space).

Anyhow, that's the request: using Christian's sample to access ROS's, can anyone with a 5100 try plugging in #$02 (i.e. values besides #$04 and #$08) and see if a difference sequence of binary is copied to RWS? If so, that should be the missing ROS. I'm not sure it'll have 6K segments also, but it should be a total of about 18K.

Last edited: