daver2

10k Member

Post #37:

U10 pin 11 is an INPUT pin and, therefore, less likely to be at fault (certainly as a result of the RAM).

What you are measuring on U10 pin 11 is the signal on the main CPU data bus. Are you saying that there are NO active TTL transitions on data bit 2?

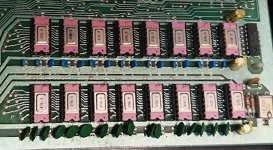

Post #39 picture #1:

Glitches can sometimes occur on the data bus. The data bus is sometimes driven (either by the CPU on a write cycle or by a device (RAM or I/O) on a read cycle). Otherwise the data bus is generally tristate and floating. During this period of time you can sometimes get crosstalk. Likewise, you can get some strange effects when buffers are enabled or disabled. Providing these occur outside of the critical timing windows for the associated CPU read or write cycle - then there should be no problem.

Post #39 picture #2:

This is strange. The problem with a digital oscilloscope is that they can create artefacts that do not exist. If you have configured the oscilloscope incorrectly, it could be showing you a 'beat frequency' arising due to a mismatch between the signal that is being measured and the oscilloscope timebase. This is especially true if the oscilloscope signal is not being triggered.

I can see three (3) distinct waveforms present in the photograph.

If you are measuring a simple waveform (like a clock signal) you should be able to trigger on the leading or trailing edge of the signal, and all should be well.

If the waveform you are measuring is not a 'simple' waveform (like a data bus), you can get strange effects displayed (visually) as the oscilloscope triggers on (say) the leading edge of a transition. If this is not the same point (in time) as the other trigger points, the waveform may not display correctly.

However, having seen this, I am going to ask the dumb question - what power supply are you using, and have you checked that the +5V supply is OK using your oscilloscope? Set the coupling to AC and apply the ground clip to a GOOD 0V point and the probe to +5V. Increase the sensitivity of the Y channel to get some noise displayed. Adjust the timebase 5ms/div and measure the peak-to-peak noise. Increase the speed of the timebase, and observe the peak-to-peak of the noise at the varying timebase speeds. At a slow timebase, we are looking for 50/60/100/120 Hz ripple (i.e. power supply capacitor problems). At the higher timebases, we are looking for noise (i.e. how good are the decoupling capacitors on the board).

For the faster timebase settings, I would also use the probe around different +5V (VCC) pins of various IC pins distributed over the PCB. You are looking for the worst peak-to-peak noise levels.

Set the probe to DC coupling and 1V/div. What is the actual DC level indicated?

TTL devices are rated at a VCC voltage between +4.75V and +5.25V. However, I would aim for +4.9V and +5.1V as being acceptable.

Details at this stage can save a whole load of problems later...

Dave

U10 pin 11 is an INPUT pin and, therefore, less likely to be at fault (certainly as a result of the RAM).

What you are measuring on U10 pin 11 is the signal on the main CPU data bus. Are you saying that there are NO active TTL transitions on data bit 2?

Post #39 picture #1:

Glitches can sometimes occur on the data bus. The data bus is sometimes driven (either by the CPU on a write cycle or by a device (RAM or I/O) on a read cycle). Otherwise the data bus is generally tristate and floating. During this period of time you can sometimes get crosstalk. Likewise, you can get some strange effects when buffers are enabled or disabled. Providing these occur outside of the critical timing windows for the associated CPU read or write cycle - then there should be no problem.

Post #39 picture #2:

This is strange. The problem with a digital oscilloscope is that they can create artefacts that do not exist. If you have configured the oscilloscope incorrectly, it could be showing you a 'beat frequency' arising due to a mismatch between the signal that is being measured and the oscilloscope timebase. This is especially true if the oscilloscope signal is not being triggered.

I can see three (3) distinct waveforms present in the photograph.

If you are measuring a simple waveform (like a clock signal) you should be able to trigger on the leading or trailing edge of the signal, and all should be well.

If the waveform you are measuring is not a 'simple' waveform (like a data bus), you can get strange effects displayed (visually) as the oscilloscope triggers on (say) the leading edge of a transition. If this is not the same point (in time) as the other trigger points, the waveform may not display correctly.

However, having seen this, I am going to ask the dumb question - what power supply are you using, and have you checked that the +5V supply is OK using your oscilloscope? Set the coupling to AC and apply the ground clip to a GOOD 0V point and the probe to +5V. Increase the sensitivity of the Y channel to get some noise displayed. Adjust the timebase 5ms/div and measure the peak-to-peak noise. Increase the speed of the timebase, and observe the peak-to-peak of the noise at the varying timebase speeds. At a slow timebase, we are looking for 50/60/100/120 Hz ripple (i.e. power supply capacitor problems). At the higher timebases, we are looking for noise (i.e. how good are the decoupling capacitors on the board).

For the faster timebase settings, I would also use the probe around different +5V (VCC) pins of various IC pins distributed over the PCB. You are looking for the worst peak-to-peak noise levels.

Set the probe to DC coupling and 1V/div. What is the actual DC level indicated?

TTL devices are rated at a VCC voltage between +4.75V and +5.25V. However, I would aim for +4.9V and +5.1V as being acceptable.

Details at this stage can save a whole load of problems later...

Dave

Last edited: