Ruud

Veteran Member

Already in 1985 I started writing my own 6502 assembler, written in Turbo Pascal. And I have been expanding it with other CPUs. I'm busy assembling this MicroKit09 and want to be able to write software for it using my own assembler. That will be an weird experience because the last time I wrote in 6809 assembly was in 1986/1987 at HTS (Technical university ???). And even then, I wrote the program but didn't even see the binary result.

Anyway, I found another multi-CPU assembler written by A.C. Verschueren, also written in Pascal. I only found this about 20 years ago and he had a complete different approach of how to compile code. But the plus, I was able to change his code so far that it would accept my source code.

Please have a look at this code:

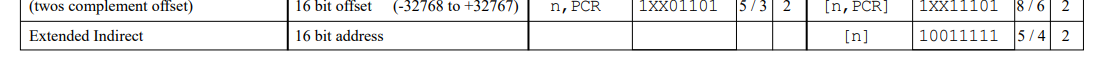

What puzzles me is the code at 006E. The lines 007A..0084 proof that if the difference is less than 128 bytes, the short method is used. But the code at 006E uses the long method although the difference is smaller than 128 bytes. The books I have are not clear enough about it and my own assumption is that the code had should been A9 9C 1A. Another thing: I saw various combinations of code using XX 9C 80..FE but never in the range 00..7F.

Can anybody confirm that or I missing something? TIA!

Anyway, I found another multi-CPU assembler written by A.C. Verschueren, also written in Pascal. I only found this about 20 years ago and he had a complete different approach of how to compile code. But the plus, I was able to change his code so far that it would accept my source code.

Please have a look at this code:

Code:

0000 3404ABE0 label5: aba ; 6800 !

....

0056 A99B label3: adca [d,x] ; indirect D offset

0058 A9F1 adca [,s++] ; indirect auto incr.

005A A9D1 adca [,u++] ; indirect auto incr.

005C A991 adca [,x++] ; indirect auto incr.

005E A9B1 adca [,y++] ; indirect auto incr.

0060 A9F3 adca [,--s] ; indirect auto incr.

0062 A9D3 adca [,--u] ; indirect auto incr.

0064 A993 adca [,--x] ; indirect auto incr.

0066 A9B3 adca [,--y] ; indirect auto incr.

0068 A99C95 adca [label5,pcr]

006B A99CE8 adca [label3,pcr]

006E A99D001A adca [label4,pcr]

0072 A99D0484 adca [label2,pcr]

0076 A9E4 adca ,s

0078 A9C4 adca ,u

007A

007A

007A A99C83 adca [label5,pcr]

007D A99C80 adca [label5,pcr]

0080 A99DFF7C adca [label5,pcr]

0084 A99DFF78 adca [label5,pcr]

0088

0088

0088 A984 adca ,x

008A A9A4 adca ,y

008C C913 label4: adcb #$13 ; immediate data

....

04FA label2:

04FA 2FFE ble label2Can anybody confirm that or I missing something? TIA!