The connectors came from Mouser and I managed to desolder the connector that was on an extender card that came with the machine. It was originally from some kind of Ampex product and was far to short to be useful.

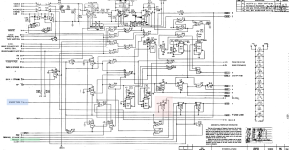

Now it was much easier to do some measurements on the machine. I started to track the RESTART signal coming from keyboard with the intention to understand why the cassette drive wasn't rewinding before it got into playback mode. The RESTART signal was first going into card A9 which is the keyboard decoder. Here a REBOOT signal is generated which passed to board A3 which is the demodulator board.

The REBOOT signal goes via a pair of flip-flops to the REWIND flip-flop Z38. It all looks good. The problem is that the END OF TAPE signal which causes Z38 immediately to be reset. The END OF TAPE signal is generated on board A2 which essentially is a selector between one signal from DECK 1 and one signal from DECK 2. The cassette decks use a LDR as the detector and a very tiny lamp mounted in the cassette guides.

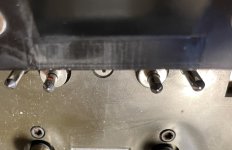

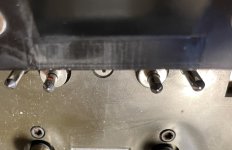

One can actually see the little lamp glowing in the picture above som the lamps were all OK.

The corresponding LDR is mounted in the hole in the tape guide. I tested with various pieces of paper to interrupt the paper and it turned out that there has to be several sheets of paper to interrupt the light so that it wasn't detected by the LDR. Could be the audio cassette that I used which had too thin media so that enough light got through to activate the LDR? Sure it was. trying with a real Datapoint data cassette gave completely different result! Now it rewound properly and started playing for a brief moment.

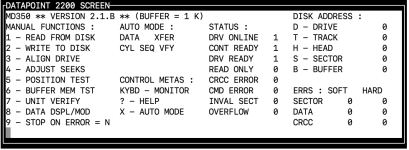

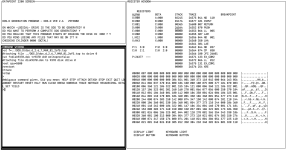

Now I need to write a proper cassette with content that can be booted on the machine. There are a number of quite short test programs on bitsavers that could be a starter for writing onto a tape. I have already tested them all in my 2200 simulator so I at least know they should dom something. I was thinking I could modify an old tape recorder to write tapes using a small STM32 uController. Possibly I could use the original drives to write tapes with proper interfacing. We'll see what is the easiest.

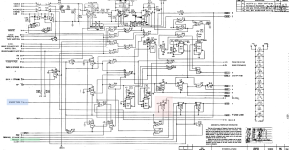

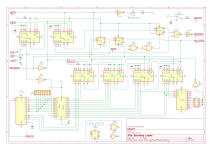

Another slightly different path is to method that was used on the Datapoint 1100 to boot from floppy. They used a circuit board which replaced board A3 and emulated the boot-loading process. Thankfully Jos Dreesen had already traced out such a board and provided me with the schematics. Thanks Jos!

The problem I don't know exactly how this thing works. From a high level perspective the boot loading process shifts bits of data one by one through pin 9 (Serdat_out / REBOOT SERIAL DATA) using the clock on pin 11 (Reboot_clk / REBOOT CLK ). A special marker on the tape is the end of record which is a stream of 11 "1" bits in a row which causes the signal 10 (Force_reboot / EOR (REBOOT)) to be flagged.

What I am not fully clear on is what the two 4 bit counter A1 and A2 fed from a 4.8 kHz clock is doing. It also seem to involve B1A, B1B and A3B. It all ends up with generating the Force_reboot / EOR (REBOOT) signal. I wonder if this is just some kind of timing network? It seems like the 74LS42 together with the S1 give the size of the ROM after which the EOR should be generated.

Also the signal TAPE MOTION is involved on pin U which I am not sure what it does. According to the schematics it comes form board A2 pin N where it is generated by a mono stable with inputs called DECK1 STROBE and DECK 2 STROBE.

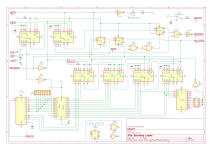

My intention is to not replicate the entire board but replace as much as possible with just a STM32 uController. It would then be easier to test different programs on the machine. I have now the option of trying to figure out all by hand or try to simulate it all in VHDL or other logic simulator unless someone else has some good input on what the logic is actually doing.