There is a place for a third 158...

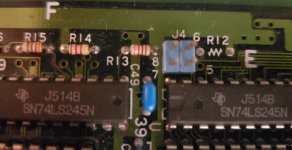

Okay, so: if you've definitively traced pin 1 on the chip sockets to a multiplexer output then that is indeed a legit sign that they at least *thought* of supporting the larger memory size. (Perhaps of note is the fact that it looks like on that XT clone schematic they *don't* waste a whole '158 for MA8 control, the insets on sheet 7 suggest they used different logic... perhaps also of note is the fact that sheet #3 doesn't show MA8 at all, suggesting the reason that the memory size selection stuff is relegated to bits of sheet 7 is this is a patch on an existing schematic originally designed just for 64k chips.) Follow pin 1 from that '158 and confirm it's common with pin 1 on the '158s on MA0-7. If *that's* true make sure there are no pull-up resistors connected that might be screwing things up. If that *all* checks out then, well, let's pretend it's good and move to the other part.

On the 5160 schematic there's a line to the '245 bidirectional buffer U9 pin 19, sheet 5 the IBM schematic calls RAMADDRSEL. (On your generic XT schematic this signal is on U13, sheet 3.) Your Sanyo undoubtedly has a similar buffer. Find out where that control line goes, it's the one that enables the CPU bus to be driven to or from the memory on the motherboard. On the 5160 schematic look at sheet 3; the line is driven through an LS00 (DMA-control-related reasons) by an output from the 24S10 PROM that has the programming to decide whether or not the planar RAM is enabled. That is a 4-bit PROM, of which three outputs are used, so... now follow the Q1 and Q2 outputs from that PROM. The schematic shows that they pass through a jumper block (That so far as I can tell exists as a fossilized remnant of support for 16k chips?) into the "A" and "B" inputs of '138s U42 and U56. This is how the CAS/RAS signals are switched to behave differently for the two chip types; the programming of the PROM, based on (I assume) the status of its A6/A7 inputs, toggles which CAS/RAS set is active for what memory area, and whether that area covers a 256k vs. 64k space.

(The Generic XT's circuitry is largely the same; its jumpering layout is a little uglier.)

Again, it's instructive to compare this to the 5150. If we trace that same RAMADDRSEL line on the 1984 schematics (64/256k system board) for the 5150 to sheet 3 of its schematic you'll see it terminates on U48, a 74LS138, that only has input lines connected to A18 and A19 so, again, its only choice is to enable the buffer when the board is in the bottom 256k of the address space. Likewise if you look at the inputs for U47 and U65 they're connected straight to A16 and A17 so there's no choice: each CAS/RAS pair covers a 64k area, no other options.

Now it's up to you to figure out if the Sanyo is *actually* hardwired as tight as the 5150. Follow the CAS/RAS lines back to where they come from (presumably also '138s) and figure out what their inputs are connected to. If they're straight through to A16 and A17 then it's hardwired for 64k no matter what A8 on the memory sockets does. If they are *not* then trace them back and find out if it's a PROM, a PAL, a bunch of random circuitry, *whatever*, that's connected to A16-A19 and has some kind of input for switching modes.

Just spitballing here, if this was a 5150 and you asked me to a way to hack it to 640k (and don't care about butchering it) I'd say try pulling the A/B pins on U47 and U65 out of their sockets, removing U48 entirely, running a few jumper wires, and programming a GAL with the following inputs:

A16-A19

ADDRSEL

DACK0BRD

These outputs:

MA8 (need to get this to pin1 on the DRAMs somehow, probably involves trace cuts)

CASRASDRVA and B (goes to A/B on U47 and U65)

RAMADDRSEL

And the appropriate memory map equations. "deadbug" the GAL somewhere, and, well, cross your fingers.

I have a suspicion the fix for the Sanyo will be about that extensive, but maybe they went the full mile building a full dual-mode decoder they never intended to use.