pbirkel@gmail.com

Veteran Member

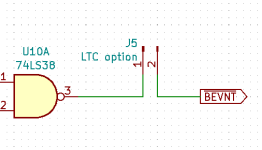

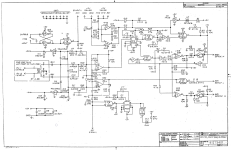

IMO it would be better to label the pins by their logical designation rather than by their physical ID. For example, meaningless "right 14a" which you have connected to "J4". I expect that the LM393 circuit is generating the LTC, being fed from an AC source on "right 14a", and being optionally connected to the backplane BEVNT via "J3" -- see the specification for this signal on http://web.frainresearch.org:8080/projects/pdp-11/q-bus.php. BE1 thus should be labeled "SSpare6" (Special Spare 6) and evidently is an AC input.

Similarly "left AP1" is BHALT and the debounce circuit around the Halt switch also then makes sense.

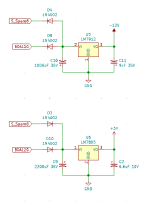

At the moment I'm assuming that all power rails are being supplied from the backplane and the two on-board regulators are uninvolved.

"right 7a / BH1" should be labeled "SSpare 8" (Special Spare 8) and is TBD as to function at this stage. In effect it's being ANDed with an AC signal that we inferred on BE1 and then being thresholded as in the case of the LTC circuit, driving a pulse generator that's going to be significant on both the rising and falling edges judging by the downstream circuitry. Three RC delays are implemented. Looking forward to seeing BDCOK and BPOK connected :->.

Perhaps "SSpare 8" comes from an external AC power switch or power fail sensor?

Similarly "left AP1" is BHALT and the debounce circuit around the Halt switch also then makes sense.

At the moment I'm assuming that all power rails are being supplied from the backplane and the two on-board regulators are uninvolved.

"right 7a / BH1" should be labeled "SSpare 8" (Special Spare 8) and is TBD as to function at this stage. In effect it's being ANDed with an AC signal that we inferred on BE1 and then being thresholded as in the case of the LTC circuit, driving a pulse generator that's going to be significant on both the rising and falling edges judging by the downstream circuitry. Three RC delays are implemented. Looking forward to seeing BDCOK and BPOK connected :->.

Perhaps "SSpare 8" comes from an external AC power switch or power fail sensor?