Thanks a lot lowen for this additional info, it's more clear now and super useful!

From the important fact of active production and since I am starting a new design I think it would be a good idea to choose an Atmel part and go for the method of converting the output file and using the ATDH1150USB.

When I started to look at these chips I didn't know about the differences so thanks, that's important.

After trying out Quartus 11 I could see after everything is assigned to the package that there are only 10 pins free now. Only few macrocells are needed. So if I want more I could indeed perhaps look at a larger chip like the ATF1508 which you linked to. This chip has a lot more pins available. I will probably order the ATF1508 and ATF1504 because I am not sure how much I will want to integrate, this also depends on test results.

I will try to find Quartus II 13.0 SP1 as you mentioned since this is newer than 11.

I have read that some of the pins can be freed if I choose not to be able to use JTAG after programming however that's not practical during development when I need to program and compare and program again each time. I could also develop using the ATF1508 and then evaluate after everything is 100% functional which chip will be the best choice on the PCB.

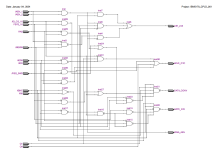

Quartus is really great to use and super elaborate, though I still need to get the procedure right of setting up a project, I was successful already to get further to be able to create the programming files(including a .POF file) of my intermediate test version of the logic.

It's pretty amazing to see how fast Quartus can break down the schematic and to see it redrawn in netlist view, and to see how it can sort out the equations in a really ordered way in the equation file. I am starting to see the huge advantages there.

I will order the ATDH1150USB and a few parts tomorrow so I can quickly get started, your advice is much appreciated, thanks!

From the important fact of active production and since I am starting a new design I think it would be a good idea to choose an Atmel part and go for the method of converting the output file and using the ATDH1150USB.

When I started to look at these chips I didn't know about the differences so thanks, that's important.

After trying out Quartus 11 I could see after everything is assigned to the package that there are only 10 pins free now. Only few macrocells are needed. So if I want more I could indeed perhaps look at a larger chip like the ATF1508 which you linked to. This chip has a lot more pins available. I will probably order the ATF1508 and ATF1504 because I am not sure how much I will want to integrate, this also depends on test results.

I will try to find Quartus II 13.0 SP1 as you mentioned since this is newer than 11.

I have read that some of the pins can be freed if I choose not to be able to use JTAG after programming however that's not practical during development when I need to program and compare and program again each time. I could also develop using the ATF1508 and then evaluate after everything is 100% functional which chip will be the best choice on the PCB.

Quartus is really great to use and super elaborate, though I still need to get the procedure right of setting up a project, I was successful already to get further to be able to create the programming files(including a .POF file) of my intermediate test version of the logic.

It's pretty amazing to see how fast Quartus can break down the schematic and to see it redrawn in netlist view, and to see how it can sort out the equations in a really ordered way in the equation file. I am starting to see the huge advantages there.

I will order the ATDH1150USB and a few parts tomorrow so I can quickly get started, your advice is much appreciated, thanks!