John(Wales-UK)

Experienced Member

- Joined

- Oct 31, 2015

- Messages

- 112

Outstanding. Many thanks for all your efforts.

| VCF West | Aug 01 - 02 2025, | CHM, Mountain View, CA |

| VCF Midwest | Sep 13 - 14 2025, | Schaumburg, IL |

| VCF Montreal | Jan 24 - 25, 2026, | RMC Saint Jean, Montreal, Canada |

| VCF SoCal | Feb 14 - 15, 2026, | Hotel Fera, Orange CA |

| VCF Southwest | May 29 - 31, 2026, | Westin Dallas Fort Worth Airport |

| VCF Southeast | June, 2026 | Atlanta, GA |

I would think a 50 mhz eZ80......

I would think a 50 mhz eZ80 with block move instructions etc could make a dent in speed problem.

An IO port write instruction to reset the ROM control bit would then revert the system to normal Model III operation.

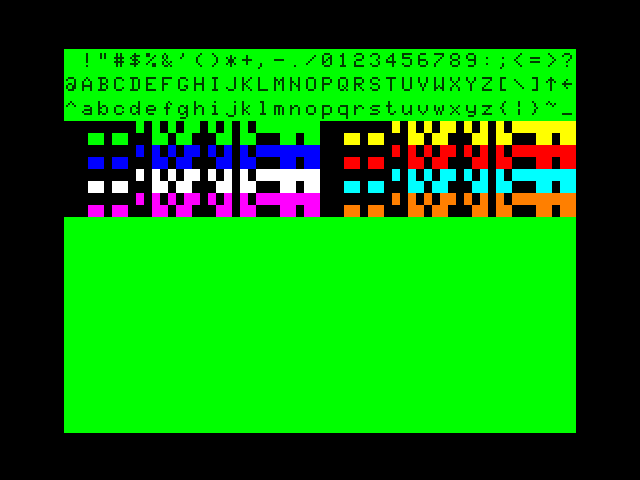

I'm currently toying with the idea of enhancing the video generator with the option of basic color, utilising unused space in the Model IIIs memory map for the colour RAM.

Though if you're switching out ROM why not make is so writing to the ROM writes to colour RAM?

If you're mapping 1K of color RAM anyway why restrict yourself to 4 bits with one for reverse video? Might as well implement a PC-style attribute set with 4 independent bits for foreground/background color. (Or if you only want 8 colors make the extra bit "blink", everybody loves that.)

Because 3 bits of colour and 1 reverse bit makes for extremely simple and straightforward circuitry, even with all of the PAL/NTSC colour encoding done with discrete logic and a few transistors. I don't think the TRS-80s graphics capabilities warrants much greater sophistication.

4 bits gives the potential for 16 colours, but 4 bits do not map to 3 primary colours to make those potential 16 colours without a pallet look-up table and DAC.

Another approach to the colour RAM, probably simplest of all, is to simply assign it to the top 1KB of the Z80s address space. OK, this would steal a whole kilobyte from the 48KB of system RAM, but how often does one sit down and type in a program that big? To prevent read contentions I would properly decode the RAM addressing so that the colour RAM properly substitutes the top 1KB of system RAM in physical hardware and does not mirror it, but the system wouldn't know the difference. "PRINT MEM" will still return "48340" and I'd still physically have a machine with 48KB of effective system RAM. Using the top 1KB of memory for program storage will just result in some funky psychedelic colour effects on screen!

Having the colour RAM mirror part of the ROM is a possible alternative option, but only in my view if the Model III BASIC operating system permits POKEs to the ROM area. For some reason I was under the impression that it doesn't, but I might be mistaken. Can anyone chime in here?

You can do RGBI with a not-much-more sophisticated resistor ladder, as long as you're happy with not-bright-yellow being a weird greenish color instead of that brown CGA monitors tweak it to.

... it's basically what you get with the Tandy Color Computer,

So far as I'm aware there is no such limitation. I think there were versions of BASIC (first version for the commodore PET?) that tried to prevent you from *PEEK*-ing BASIC, but I'm not sure what the logic would be for preventing a poke.

I guess to be 100% sure one would have to probe the Z80 control lines to see if it is doing a phantom write when POKEing to ROM. I do want to be able to read the colour RAM, which will have to be found a workaround if it is to mirror the ROM area.