Started on this 3032 today.

1. With onboard ROM and RAM the machine won't boot, though the random display screen shows.

2. With all ROMs and IO chips out and with a RAM/ROM replacement board, mapped to BASIC 4 and 32KB of RAM, the machine boots to the BASIC 4 boot screen (but clearly no flashing cursor).

######################################

3. With all ROMs and IO chips out and with a RAM/ROM replacement board, mapped to BASIC 2 and 32KB of RAM, the machine boots to a blank screen.

4. With all ROMs out and with a RAM/ROM replacement board, mapped to BASIC 2 and 32KB of RAM - and with a 6522 installed, the machine boots to the BASIC 2 boot screen (but clearly no flashing cursor).

.

@daver2 , I specifically tested the above (2 & 3) to confirm what we saw in the recent 2001 repair, viz. with all ROMs in place, but no IO chips, BASIC 4 will boot to the BASIC screen but BASIC 2 will only show a blank screen. With a 6522 installed, BASIC 2 will then show the BASIC boot screen. I.e. a 6522 (but not the 6520s) are needed to get to the BASIC 2 startup screen. Just a point of interest.

######################################

.

Anyways, back to this machine and here is the bit of interest:

.

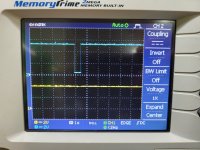

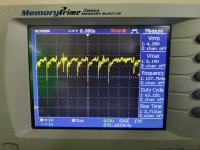

5. With a working Kernal and PETTESTER V4 I get the first PETTESTER screen. However, it never goes past this screen / test. Just stays here.

My understanding is that this means PETTESTER is not passing the VDU test. However, I cannot, for the life of me figure out what is failing. The PETTESTER screen seems stable (no characters changing, etc.), I've confirmed the two 2114s are fine and when the machine boots into BASIC, I get a clean screen with just the expected BASIC boot screen.

.

I've also tested and replaced all 4116s that failed in my memory tester. But I also get the same with a RAM board mapping the RAM out, i.e. PETTESTER never goes past this first screen with either mapped out RAM or the onboard RAM.

Any ideas?

1. With onboard ROM and RAM the machine won't boot, though the random display screen shows.

2. With all ROMs and IO chips out and with a RAM/ROM replacement board, mapped to BASIC 4 and 32KB of RAM, the machine boots to the BASIC 4 boot screen (but clearly no flashing cursor).

######################################

3. With all ROMs and IO chips out and with a RAM/ROM replacement board, mapped to BASIC 2 and 32KB of RAM, the machine boots to a blank screen.

4. With all ROMs out and with a RAM/ROM replacement board, mapped to BASIC 2 and 32KB of RAM - and with a 6522 installed, the machine boots to the BASIC 2 boot screen (but clearly no flashing cursor).

.

@daver2 , I specifically tested the above (2 & 3) to confirm what we saw in the recent 2001 repair, viz. with all ROMs in place, but no IO chips, BASIC 4 will boot to the BASIC screen but BASIC 2 will only show a blank screen. With a 6522 installed, BASIC 2 will then show the BASIC boot screen. I.e. a 6522 (but not the 6520s) are needed to get to the BASIC 2 startup screen. Just a point of interest.

######################################

.

Anyways, back to this machine and here is the bit of interest:

.

5. With a working Kernal and PETTESTER V4 I get the first PETTESTER screen. However, it never goes past this screen / test. Just stays here.

My understanding is that this means PETTESTER is not passing the VDU test. However, I cannot, for the life of me figure out what is failing. The PETTESTER screen seems stable (no characters changing, etc.), I've confirmed the two 2114s are fine and when the machine boots into BASIC, I get a clean screen with just the expected BASIC boot screen.

.

I've also tested and replaced all 4116s that failed in my memory tester. But I also get the same with a RAM board mapping the RAM out, i.e. PETTESTER never goes past this first screen with either mapped out RAM or the onboard RAM.

Any ideas?