The problem with all of these is the lack of documentation related to the test vectors that are used to check a device - or the percentage of test coverage.

We have previously identified that some pins of a couple of 74 devices are not tested with certain testers.

I had the same issue with one of our repair companies we use at work. We had a fault on a board. They plugged it into their test rig, and it passed.

When I had a look at the test rig, it didn't actually test this input signal!

Once I had explained to the test engineer what this input actually did, he was able to modify the test vectors to test this input and, lo and behold, the card failed this time.

A bit of poking with an oscilloscope and we found the faulty package and the board was working once again.

Of course, this meant that all the boards of this type that had been previously repaired/tested had not had this input signal (or the associated logic) tested either.

Just a warning not to believe any piece of test equipment at total face value (especially at the budget end of the market)...

Dave

the "Lack of documentation" remark is very telling.

A good example of this is the TTL IC testers on ebay which claim to test 74 series IC's.

The designers of some of these need to go back to school in a time machine and get a lesson from an Engineer at Texas instruments back in 1969. The engineer had pens in his pocket and a suit, with a thin black tie and a white shirt and generally always carried an HP calculator, like the HP-25 (with RPN).

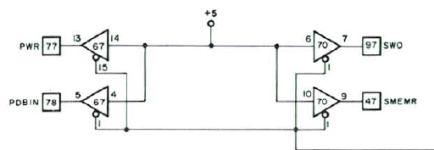

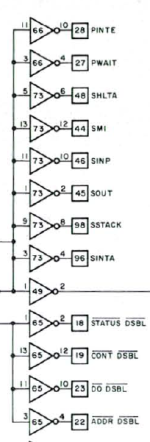

The modern conceived tester protocols could not imagine a chip like the SN7425, it had a control (strobe ) pin, that enables or disables the gates withing the package. A lot of TTL IC's had such strobe pins, with input current levels that were not like a single TTL input pin.

The strobe pin is enabling or disabling 4 of the inputs to each gate in the SN7425, not one, the current sinking on that pin, to create a logic low is x4 the normal value for a 74 chip TTL input.

The tester is "not prepared for this" and reports the chip as defective. However, because 74LS series chips (or HC, HCT etc) have lower input currents, the tester, likely tests these as ok. When in reality both are ok.

Other testers I have bought for testing Memory chips in vintage computers have been equally as disappointing. Malfunctioning and declaring higher speed chips as failed when they are perfectly good.

What I'm saying here is that you can take a lot of modern IC tester results, with a grain of salt, especially if they have been programmed on devices like Arduinos by latter day Engineers, who did no grow up with with the 1970's style TTL technology, because there are many nuances that they are oblivious to in this vintage tech, and sooner or later, that will catch them out. They can still be excellent programmers though, no dispute there.

If you could find a TTL IC tester made in 1980, it might be another story and give you reliable results.

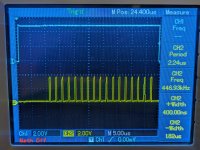

Still, I generally I don't bother with IC testers for standard 74 series TTL's because, it is actually better to check them in circuit, with the scope, to ensure they are obeying their logic table. This is testing them in the circuit they were designed to run in and were known to run in, in my view it is mainly the better test method for these vintage parts.

Still, when it comes to IC testers, in my experience at least, it is more likely they will test a good parts as failed, rather than the reverse. So it is interesting that your IC tester, tested the 74157's as ok. So, despite being counterfeit, they are possibly ok functionally.