mmruzek

Experienced Member

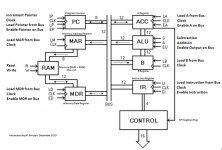

Hi, I have built a homebrew computer using TTL IC's according to the architecture described by Eckert in his paper "Microprogrammed Versus Hardwired Control Units: How Computers Really Work". The architecture is shown in the attached diagram. It is a fairly basic machine with a 12 bit bus consisting of 8 data bits and 4 control bits. I built a hardwired controller for my first pass, and am in the process of doing some testing. To do the testing I am hand coding to create hex files that go into a 'ROM A' and 'ROM B'

The computer has 8 possible instructions. They are:

Symbol, Hex Value, Description

LDA* 1 Load Accumulator with data from the address given

STA* 2 Store Accumulator data at the address given

ADD 3 Add B to the Accumulator, store in Accumulutor

SUB 4 Subtract B from the Accumulator, store in Accumulator

MBA 5 Copy Accumulator to B

JMP* 6 Jump to new program count (Program counter modified)

JN* 7 Jump if negative flag is set. (Program counter modified)

HLT 8-F Halt by stopping clock. (Not currently functional)

‘Fetch’ N/A Clock ticks 0, 1 and 2 always load the next instruction

*Any command with an asterik requires a ‘ROM A’ address or program count value in the first 8 bits.

So, basically I am at the starting point of creating a working language from these commands. Before I proceed with that I started wondering if these 8 instructions are the best choice from a practical point of view. It would be easy enough for me to substitute or change an instruction at this point... so I am wondering if anyone has some thoughts about this? Probably my biggest concern is the conditional jump is based on the negative flag being set.

More information about the project is here

http://www.mtmscientific.com/stack.html

Michael

The computer has 8 possible instructions. They are:

Symbol, Hex Value, Description

LDA* 1 Load Accumulator with data from the address given

STA* 2 Store Accumulator data at the address given

ADD 3 Add B to the Accumulator, store in Accumulutor

SUB 4 Subtract B from the Accumulator, store in Accumulator

MBA 5 Copy Accumulator to B

JMP* 6 Jump to new program count (Program counter modified)

JN* 7 Jump if negative flag is set. (Program counter modified)

HLT 8-F Halt by stopping clock. (Not currently functional)

‘Fetch’ N/A Clock ticks 0, 1 and 2 always load the next instruction

*Any command with an asterik requires a ‘ROM A’ address or program count value in the first 8 bits.

So, basically I am at the starting point of creating a working language from these commands. Before I proceed with that I started wondering if these 8 instructions are the best choice from a practical point of view. It would be easy enough for me to substitute or change an instruction at this point... so I am wondering if anyone has some thoughts about this? Probably my biggest concern is the conditional jump is based on the negative flag being set.

More information about the project is here

http://www.mtmscientific.com/stack.html

Michael