T-Squared

Veteran Member

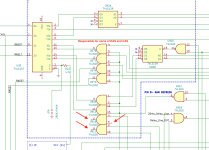

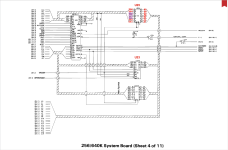

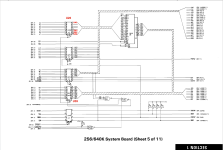

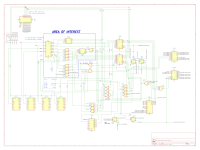

Okay, looking closer at the memory datasheet and this page, I found that the timing for the RAS-CAS-WE cycle seems to be within the proper range of at least 200ns.

Still, I'm still confused, and we're back to square one as to why the data disappears. (Which is probably what is causing address 0001 to fail)

I couldn't read the Refresh Gate with my logic analyzer, for some reason, even though I seem to have found it in my own schematic. I may figure that out later in the day tomorrow.

Still, I'm still confused, and we're back to square one as to why the data disappears. (Which is probably what is causing address 0001 to fail)

I couldn't read the Refresh Gate with my logic analyzer, for some reason, even though I seem to have found it in my own schematic. I may figure that out later in the day tomorrow.

Last edited: