All right, I've taken a look. I think I might be getting the hang of the basics.

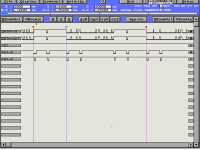

My multimeter does not show that the data pins between in and out are substantially connected; it reads 4 megaohms.

I also found a way to expand the data bus (instead of outputting 1 when the hex value is detected)

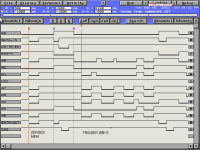

In 256k mode:

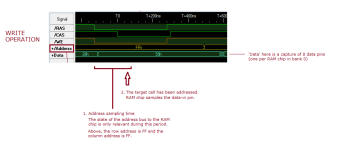

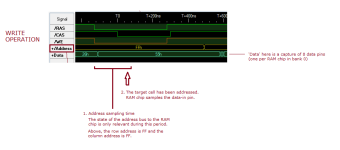

1. It's complicated, but Data-In and Data-Out looks the same as the Read-Write-Cycle diagrams in the memory I'm using (NEC D41256C)

2. The binary values on each 8-bit data bus (in and out) seem to match what MacOS' programmer calculator shows me. (i.e. 01010101 for 55h, and 10101010 for AAh)

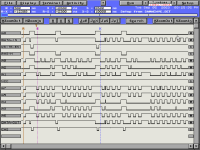

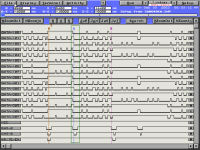

In 640k mode:

Same. HOWEVER...

I believe I have found our culprit!

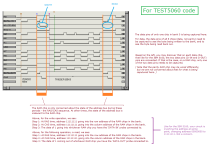

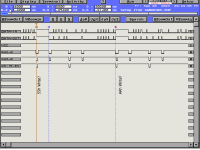

In 256k mode, if I am reading this correctly,

The memory value 55h is written (Cursor R, WRITE_EN is low), and is correctly read (When RAS and CAS are asserted the second time at Cursor X)

Same when it's written with AAh when written (Cursor S), and when read.

But in 640k mode...

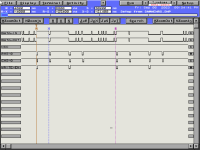

But in 640k mode...

WHERE'S MY DATA?! (Highlighted in Green, at Cursor X)

Value 55h is missing when RAS and CAS are asserted!

Another problem that may have arisen, CAS seems to have shifted! (It doesn't start halfway through RAS assertion, or terminate at its rising edge, which is what the data sheet says its supposed to do!)

Strangely, Value AAh seems to be fine, as you can see after Cursor S on the second capture.