Does anyone know if it's possible to add on additional PCI slots to a PCI bus, with out a PCI-to-PCI bridge?

Ive seen loads of single angled straight-through risers and loads of proprietary versions. The closest thing I've found is this:

https://www.ebay.com/itm/3-Slot-PCI-32-Bit-Passive-Riser-Card-PCI3-B1-2U-000-57270-AR-/181625270319

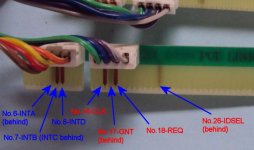

But it has flyleads. As far as I can see these fly-leads go to the INTA# - INTD# pins.

Are PCI slots not a straight-through bus? I've googled around but even adding "-pcie" nearly everything is about pcie now.

Ive seen loads of single angled straight-through risers and loads of proprietary versions. The closest thing I've found is this:

https://www.ebay.com/itm/3-Slot-PCI-32-Bit-Passive-Riser-Card-PCI3-B1-2U-000-57270-AR-/181625270319

But it has flyleads. As far as I can see these fly-leads go to the INTA# - INTD# pins.

Are PCI slots not a straight-through bus? I've googled around but even adding "-pcie" nearly everything is about pcie now.