Hi,

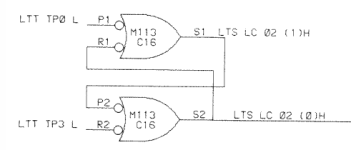

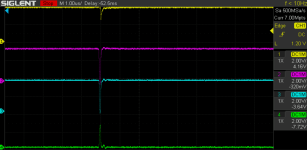

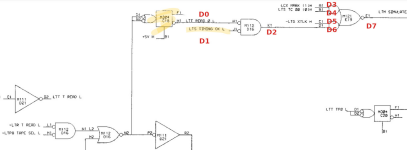

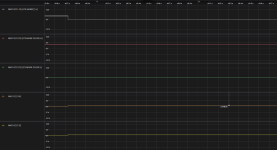

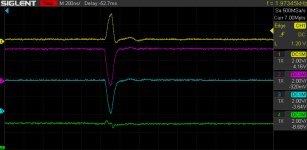

@antiquekid3 -- we used the scope today to look at the NOR clock in C16 that generates LC 02. Our scope does 500Ms/s with four probes in use.

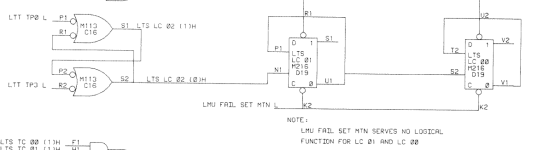

Yellow - C16 S1 LTS LC 02 (1) H

Pink - C16 R2 LTT TP3 L

Blue - C16 P1 LTT TP0 L

Green - C16 S2 LC 02 (0) H

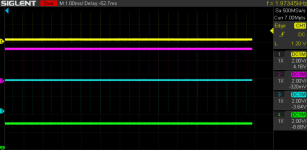

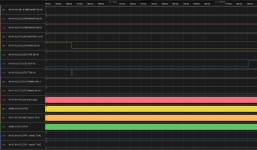

Here's what it looks like running

@ZachyCatGames 's code; notice the yellow, pink, and blue pulses, which are pretty tall, and the green pulses, which are quite short.

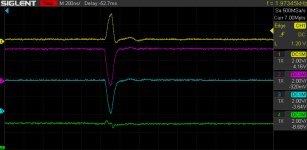

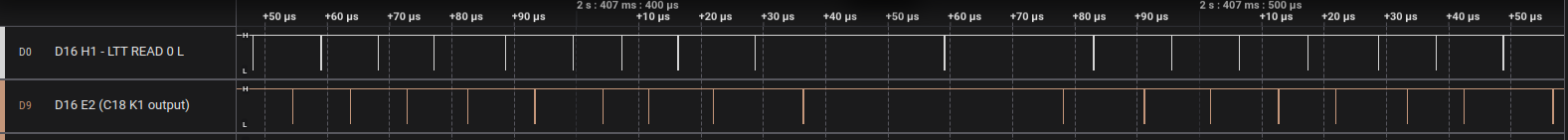

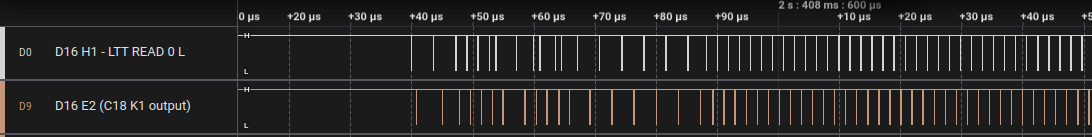

Zooming in one one of those clock ticks, we see:

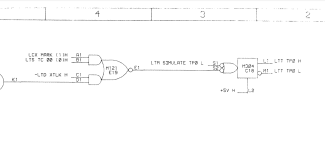

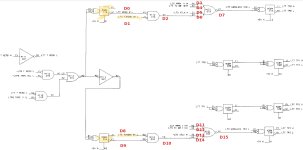

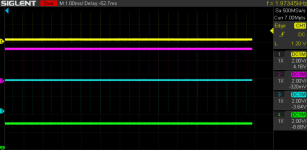

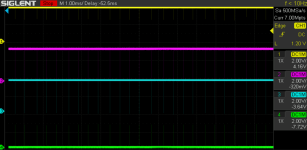

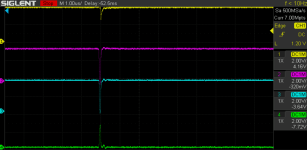

Thinking that maybe the short green signal is a marginal signal from one of the ICs, we found yet another M113 to swap in (this time, from A26). When we run the test with this other M113, we get a signal that we think looks a lot better -- nice spikes on all four channels:

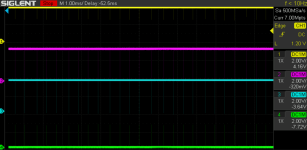

Again zooming in on one "tick":

Does that look right to you? We notice that, in the latter images, yellow (S1) switches from default low to default high (i.e., yellow is high and "dips" instead of being low with "raises"). I was thinking this might be because (in the latter images) S2 is actually working correctly.

In this state, the machine seemed to generate the Tape Word FF signal pretty consistently. (We could not confirm that it was exactly right, and we didn't try running Mark 12, becuase the A24 M113 we borrowed was also tape related.)

Next, we ran the FC tester on the M113s that were not generating the S2 signal correctly, but both M113s passed the tester in multiple runs. Zach also tried changing the test delays but that did not seem to affect anything.

One super weird thing happened when we were working with the FCT. When we plugged one of the M113s into the tester, the UUT power light would come on dimly, even when the power was switched off. (The UUT power light would light up to its normal brightness when we switched the power on.) Is this indicative of anything? We confirmed this happening a few times, but then it stopped happening before I could get pictures and we haven't been able to replicate it since. (

@vrs42 have you seen this happen before?)

This was all so weird that we will probably try to recreate everything again tomorrow or Wednesday to make sure that we aren't crazy.

We wondered if we should maybe try scoping the S2 pin while the FCT is running to see if we are getting weak signals from the S2 pin. How do we do that?

Finally, if the M113s are actually putting out good signals on the S2 pins, is the next thing to look at the flip chip slot itself? Can I spray deoxit straight into the FC slot? Or what is the right method for cleaning slots? Since we are probing directly from the pins all on the same slot, I wouldn't think that it is a wire wrap issue.

Sincerely,

Dumbfounded in Duluth