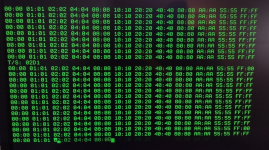

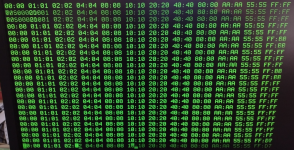

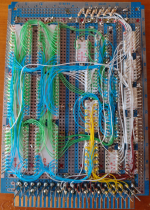

Doug, I was sitting and thinking, and thought, what if it is a bit pattern thing. So I made some changes using the these patterns (F0, 0F, A0, 0A, 50, 05, A5, 5A, 00, FF, AA, 55) and in that order. Oddly enough, the problem was still with FF. My next test is going to be a F4, F5, F6, F7, F8, F9, FA, FB, FC, FD, FE, FF pattern. And then that in reverse. And then swapping the digits to be 4F, 5F, 6F, 7F, 8F, 9F, AF, BF, CF, DF, EF, FF. and then swap those digits. I suspect that the problem will always show with the FF pattern no matter where it is. So, who knows. And since I also have an extender card, I may put the board on an extender to see if that changes anything. Debugging is so much fun! LOL