MykeLawson

Veteran Member

- Joined

- Mar 20, 2014

- Messages

- 539

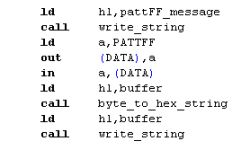

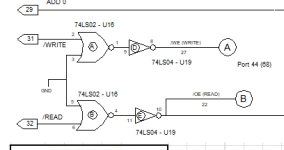

Well, best I can do is an o'scope. I've completely replaced all the memory chips and both '244 buss drivers. I removed all but the first memory chip in the hope it was a loading issue. Interestingly, a previous test I ran left the FF pattern in memory when it was completed. I whipped up a quick BASIC program (slower and 'no assembly required') and sure enough, it read all FF's without issue. So, I think I'm going to run a test where I write a pattern to the memory cells, but instead to reading them to be converted for display, I'll write them to system memory. Then I can just read them from the routine in the system monitor. I'm just trying to get all the info I can.