daver2

10k Member

Nope, you don’t need to change anything in the ROM.

Did you download my manual and read it? If in doubt, read the manual...

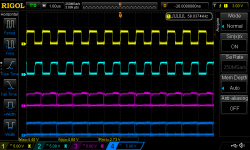

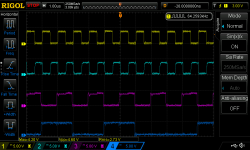

It looks like every other character is formed correctly. This could imply there is a fault with either the ODD or EVEN side of the video RAM.

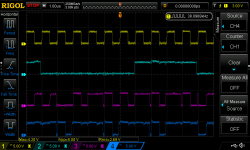

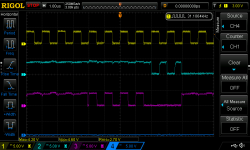

I do see the odd German characters with umlauts, but some of the individual characters look like Romulan - implying the character generator ROM socket is not making good contact with pins of the ROM or the character generator is partially faulty.

My PETTESTER stores the characters sequentially from $00 to $FF into the video RAM, so if you check the Commodore PET documentation for the German character set you may be able to see some patterns forming.

Is that a ‘bespoke’ character generator I see on the board?

Dave

Did you download my manual and read it? If in doubt, read the manual...

It looks like every other character is formed correctly. This could imply there is a fault with either the ODD or EVEN side of the video RAM.

I do see the odd German characters with umlauts, but some of the individual characters look like Romulan - implying the character generator ROM socket is not making good contact with pins of the ROM or the character generator is partially faulty.

My PETTESTER stores the characters sequentially from $00 to $FF into the video RAM, so if you check the Commodore PET documentation for the German character set you may be able to see some patterns forming.

Is that a ‘bespoke’ character generator I see on the board?

Dave