modem7

10k Member

I took a quick look at the circuit diagram in post #110, looking at just the circuitry that generates the lines you have marked as CAS0 and CAS1.

I can see that in the 640KB configuration (JP6 jumper in), the 256Kbit chips go into the two banks associated with the lines that you have marked as CAS0 and CAS1.

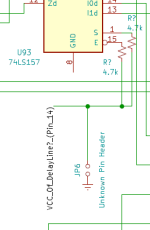

Taking a quick look elsewhere in the diagram, I spotted an error. See the red line at [here]. None of the connected pins is an output.

I can see that in the 640KB configuration (JP6 jumper in), the 256Kbit chips go into the two banks associated with the lines that you have marked as CAS0 and CAS1.

Taking a quick look elsewhere in the diagram, I spotted an error. See the red line at [here]. None of the connected pins is an output.